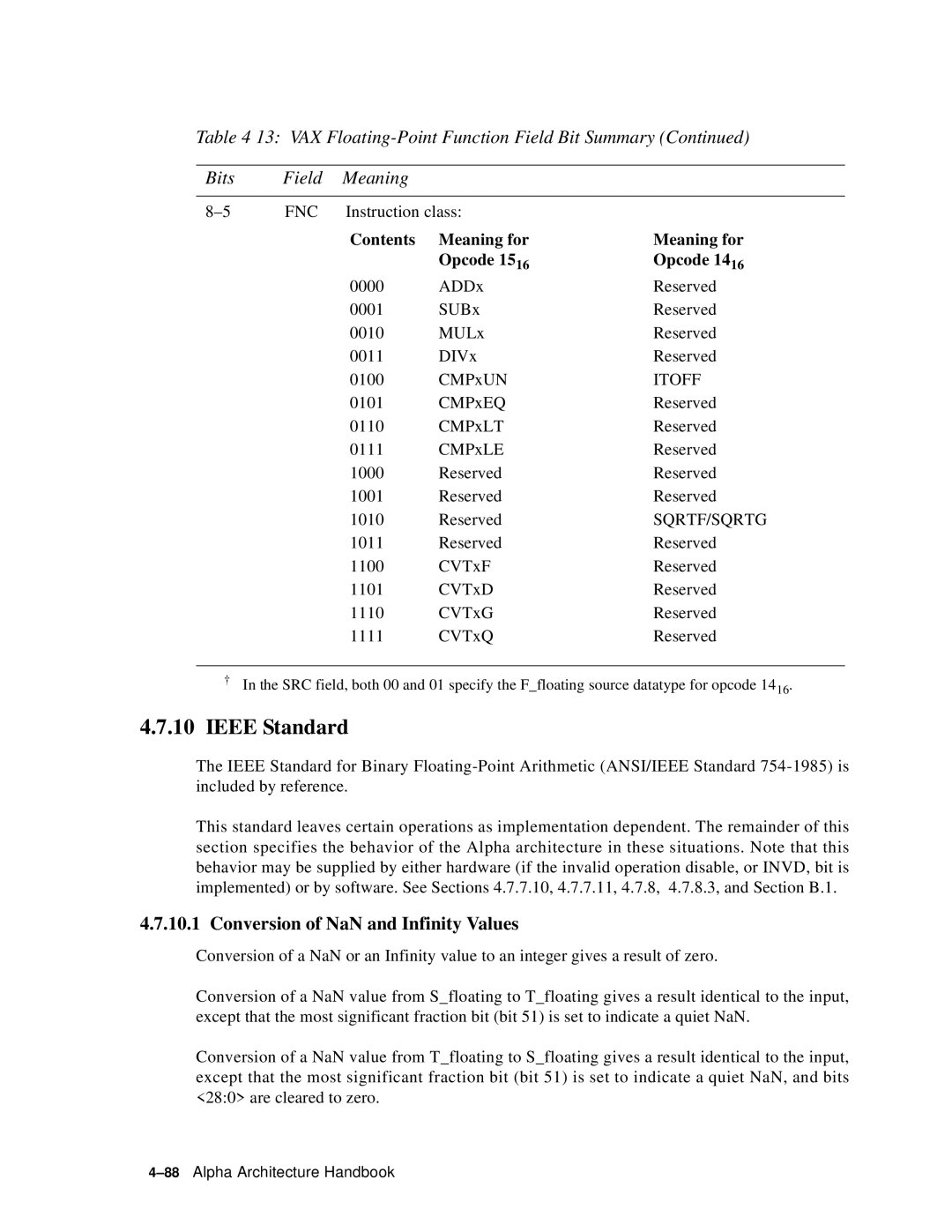

Table

Bits | Field | Meaning |

|

|

|

|

|

| |

FNC | Instruction class: |

| ||

|

| Contents | Meaning for | Meaning for |

|

|

| Opcode 1516 | Opcode 1416 |

|

| 0000 | ADDx | Reserved |

|

| 0001 | SUBx | Reserved |

|

| 0010 | MULx | Reserved |

|

| 0011 | DIVx | Reserved |

|

| 0100 | CMPxUN | ITOFF |

|

| 0101 | CMPxEQ | Reserved |

|

| 0110 | CMPxLT | Reserved |

|

| 0111 | CMPxLE | Reserved |

|

| 1000 | Reserved | Reserved |

|

| 1001 | Reserved | Reserved |

|

| 1010 | Reserved | SQRTF/SQRTG |

|

| 1011 | Reserved | Reserved |

|

| 1100 | CVTxF | Reserved |

|

| 1101 | CVTxD | Reserved |

|

| 1110 | CVTxG | Reserved |

|

| 1111 | CVTxQ | Reserved |

†In the SRC field, both 00 and 01 specify the F_floating source datatype for opcode 1416.

4.7.10IEEE Standard

The IEEE Standard for Binary

This standard leaves certain operations as implementation dependent. The remainder of this section specifies the behavior of the Alpha architecture in these situations. Note that this behavior may be supplied by either hardware (if the invalid operation disable, or INVD, bit is implemented) or by software. See Sections 4.7.7.10, 4.7.7.11, 4.7.8, 4.7.8.3, and Section B.1.

4.7.10.1 Conversion of NaN and Infinity Values

Conversion of a NaN or an Infinity value to an integer gives a result of zero.

Conversion of a NaN value from S_floating to T_floating gives a result identical to the input, except that the most significant fraction bit (bit 51) is set to indicate a quiet NaN.

Conversion of a NaN value from T_floating to S_floating gives a result identical to the input, except that the most significant fraction bit (bit 51) is set to indicate a quiet NaN, and bits <28:0> are cleared to zero.