4.2 Memory Integer Load/Store Instructions

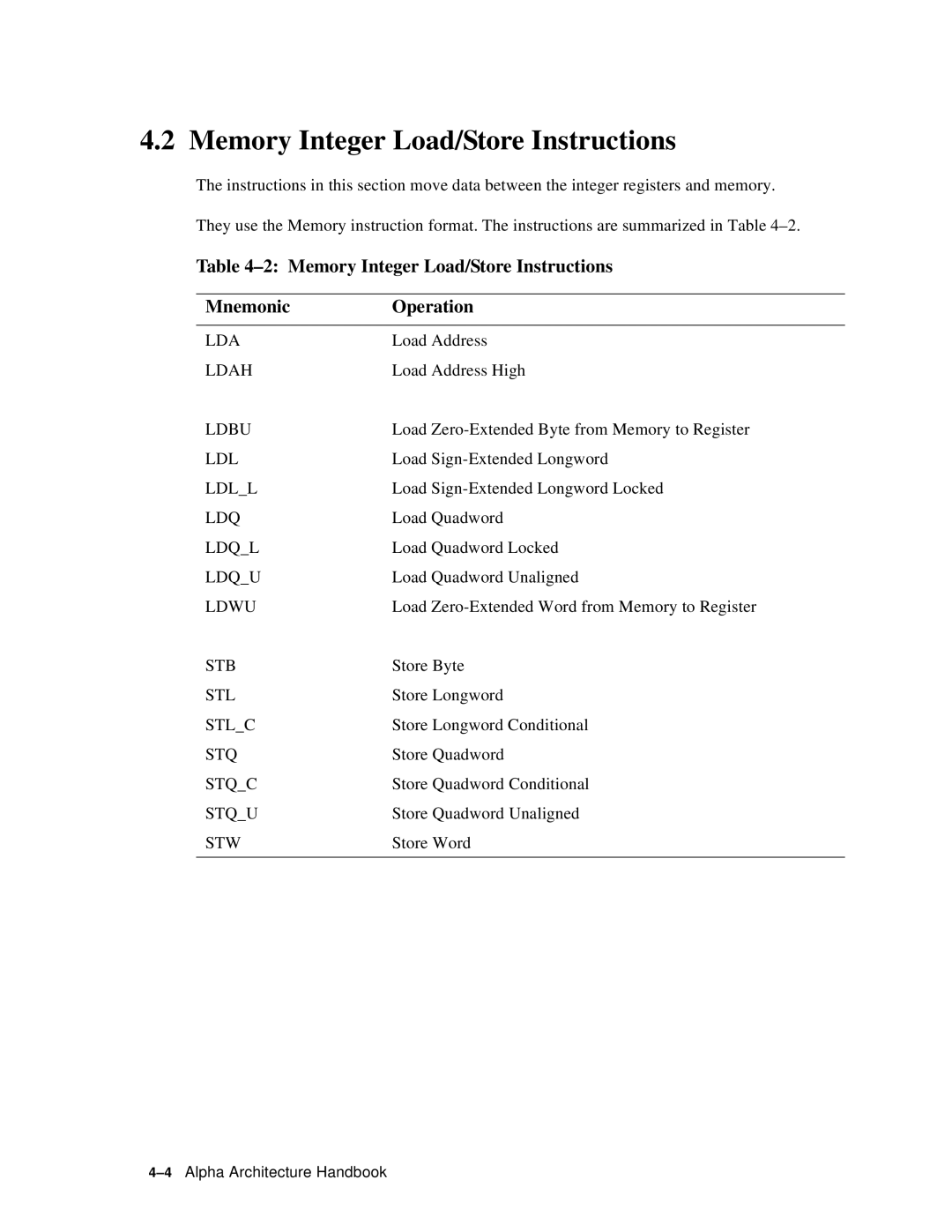

The instructions in this section move data between the integer registers and memory.

They use the Memory instruction format. The instructions are summarized in Table

Table 4–2: Memory Integer Load/Store Instructions

Mnemonic | Operation |

|

|

LDA | Load Address |

LDAH | Load Address High |

LDBU | Load |

LDL | Load |

LDL_L | Load |

LDQ | Load Quadword |

LDQ_L | Load Quadword Locked |

LDQ_U | Load Quadword Unaligned |

LDWU | Load |

STB | Store Byte |

STL | Store Longword |

STL_C | Store Longword Conditional |

STQ | Store Quadword |

STQ_C | Store Quadword Conditional |

STQ_U | Store Quadword Unaligned |

STW | Store Word |

|

|