4.11.5 Prefetch Data

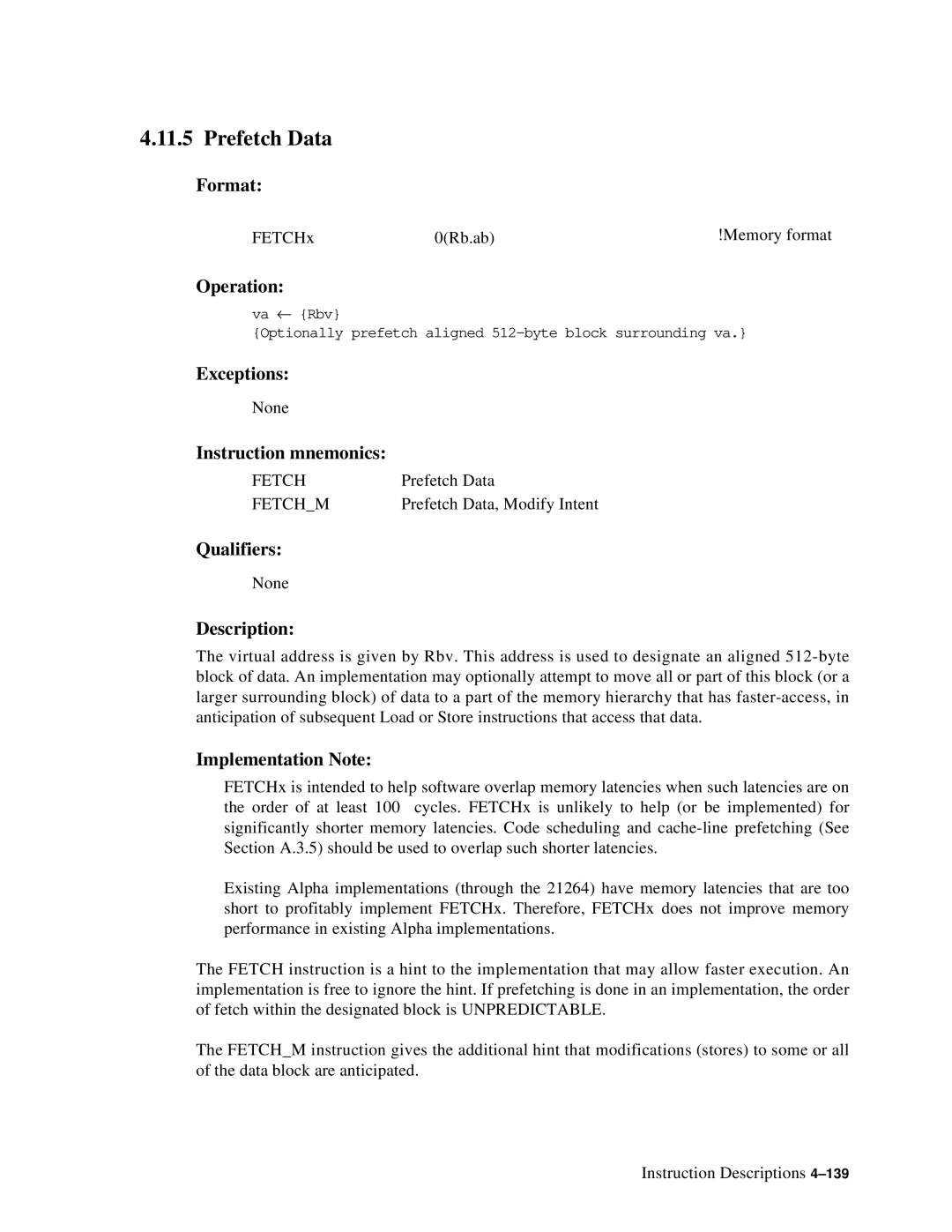

Format:

FETCHx | 0(Rb.ab) | !Memory format |

Operation:

va ← {Rbv}

{Optionally prefetch aligned

Exceptions: |

|

None |

|

Instruction mnemonics: |

|

FETCH | Prefetch Data |

FETCH_M | Prefetch Data, Modify Intent |

Qualifiers: |

|

None |

|

Description:

The virtual address is given by Rbv. This address is used to designate an aligned

Implementation Note:

FETCHx is intended to help software overlap memory latencies when such latencies are on the order of at least 100 cycles. FETCHx is unlikely to help (or be implemented) for significantly shorter memory latencies. Code scheduling and

Existing Alpha implementations (through the 21264) have memory latencies that are too short to profitably implement FETCHx. Therefore, FETCHx does not improve memory performance in existing Alpha implementations.

The FETCH instruction is a hint to the implementation that may allow faster execution. An implementation is free to ignore the hint. If prefetching is done in an implementation, the order of fetch within the designated block is UNPREDICTABLE.

The FETCH_M instruction gives the additional hint that modifications (stores) to some or all of the data block are anticipated.

Instruction Descriptions