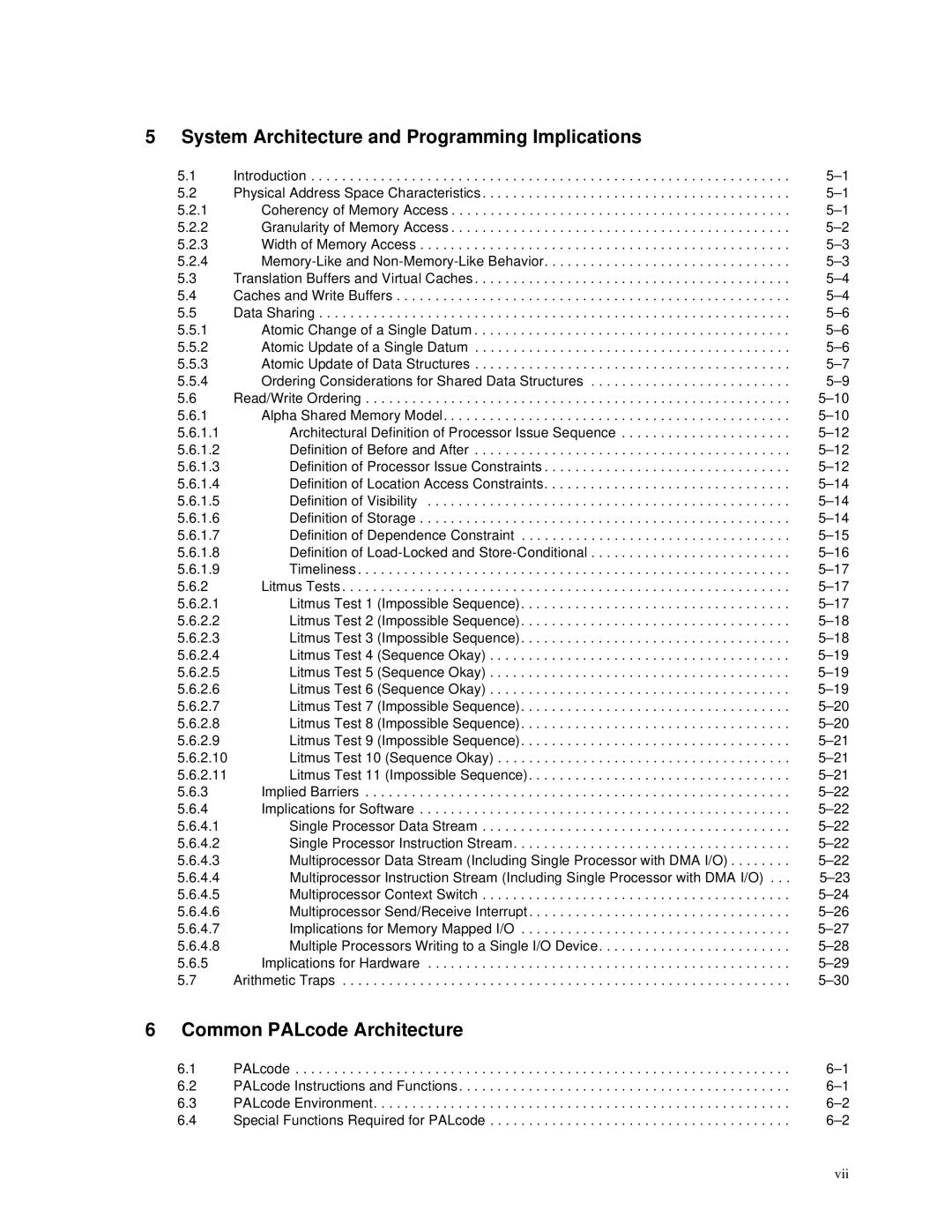

5 | System Architecture and Programming Implications |

| |

| 5.1 | Introduction | |

| 5.2 | Physical Address Space Characteristics | |

| 5.2.1 | Coherency of Memory Access | |

| 5.2.2 | Granularity of Memory Access | |

| 5.2.3 | Width of Memory Access | |

| 5.2.4 | ||

| 5.3 | Translation Buffers and Virtual Caches | |

| 5.4 | Caches and Write Buffers | |

| 5.5 | Data Sharing | |

| 5.5.1 | Atomic Change of a Single Datum | |

| 5.5.2 | Atomic Update of a Single Datum | |

| 5.5.3 | Atomic Update of Data Structures | |

| 5.5.4 | Ordering Considerations for Shared Data Structures | |

| 5.6 | Read/Write Ordering | |

| 5.6.1 | Alpha Shared Memory Model | |

| 5.6.1.1 | Architectural Definition of Processor Issue Sequence | |

| 5.6.1.2 | Definition of Before and After | |

| 5.6.1.3 | Definition of Processor Issue Constraints | |

| 5.6.1.4 | Definition of Location Access Constraints | |

| 5.6.1.5 | Definition of Visibility | |

| 5.6.1.6 | Definition of Storage | |

| 5.6.1.7 | Definition of Dependence Constraint | |

| 5.6.1.8 | Definition of | |

| 5.6.1.9 | Timeliness | |

| 5.6.2 | Litmus Tests | |

| 5.6.2.1 | Litmus Test 1 (Impossible Sequence) | |

| 5.6.2.2 | Litmus Test 2 (Impossible Sequence) | |

| 5.6.2.3 | Litmus Test 3 (Impossible Sequence) | |

| 5.6.2.4 | Litmus Test 4 (Sequence Okay) | |

| 5.6.2.5 | Litmus Test 5 (Sequence Okay) | |

| 5.6.2.6 | Litmus Test 6 (Sequence Okay) | |

| 5.6.2.7 | Litmus Test 7 (Impossible Sequence) | |

| 5.6.2.8 | Litmus Test 8 (Impossible Sequence) | |

| 5.6.2.9 | Litmus Test 9 (Impossible Sequence) | |

| 5.6.2.10 | Litmus Test 10 (Sequence Okay) | |

| 5.6.2.11 | Litmus Test 11 (Impossible Sequence) | |

| 5.6.3 | Implied Barriers | |

| 5.6.4 | Implications for Software | |

| 5.6.4.1 | Single Processor Data Stream | |

| 5.6.4.2 | Single Processor Instruction Stream | |

| 5.6.4.3 | Multiprocessor Data Stream (Including Single Processor with DMA I/O) | |

| 5.6.4.4 | Multiprocessor Instruction Stream (Including Single Processor with DMA I/O) . . . | |

| 5.6.4.5 | Multiprocessor Context Switch | |

| 5.6.4.6 | Multiprocessor Send/Receive Interrupt | |

| 5.6.4.7 | Implications for Memory Mapped I/O | |

| 5.6.4.8 | Multiple Processors Writing to a Single I/O Device | |

| 5.6.5 | Implications for Hardware | |

| 5.7 | Arithmetic Traps | |

6 Common PALcode Architecture

6.1 | PALcode | |

6.2 | PALcode Instructions and Functions | |

6.3 | PALcode Environment | |

6.4 | Special Functions Required for PALcode |

vii