The WMB instruction is the preferred method for providing

Notes:

WMB is useful for ordering streams of writes to a

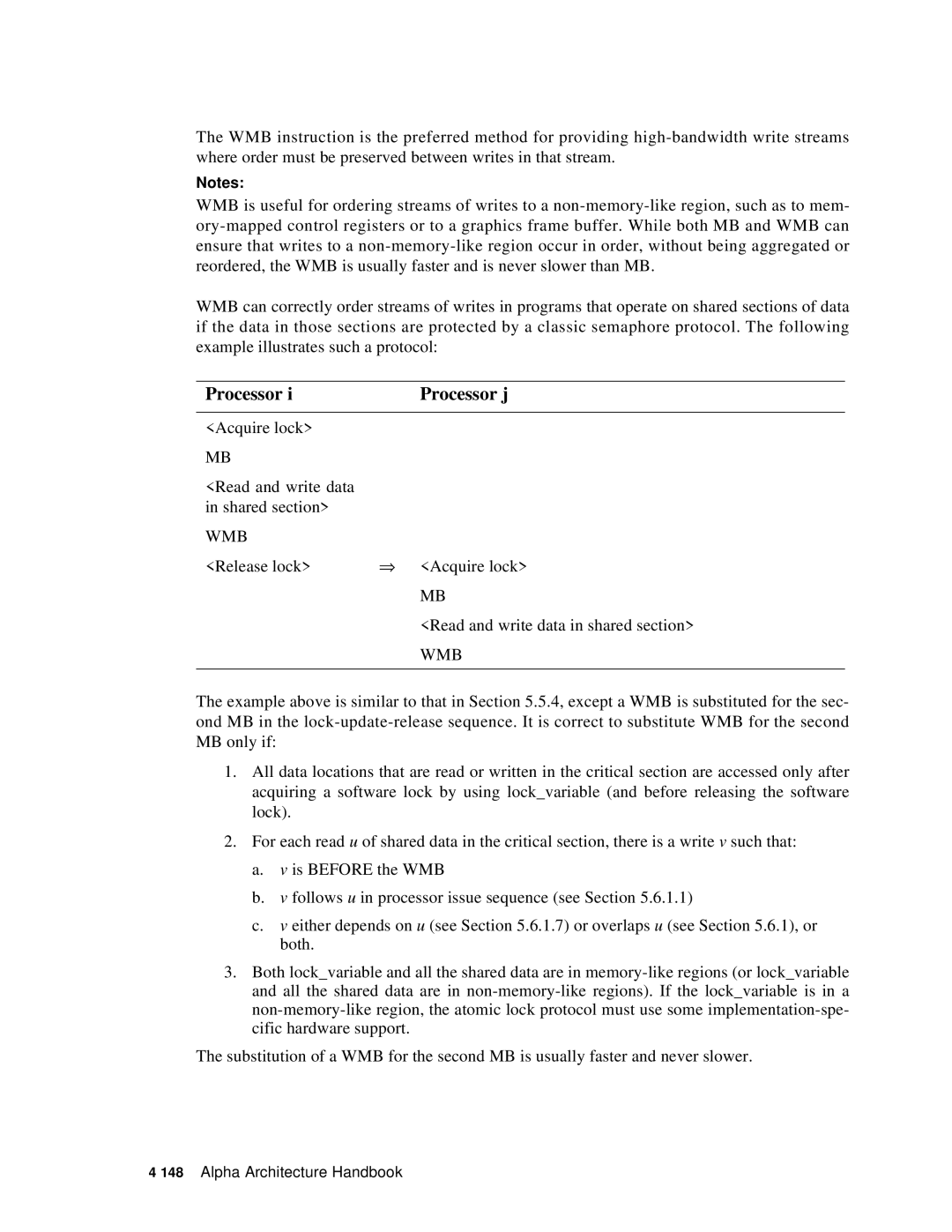

WMB can correctly order streams of writes in programs that operate on shared sections of data if the data in those sections are protected by a classic semaphore protocol. The following example illustrates such a protocol:

Processor i | Processor j |

|

|

<Acquire lock> |

|

MB |

|

<Read and write data |

|

in shared section> |

|

WMB |

|

<Release lock> | ⇒ <Acquire lock> |

| MB |

| <Read and write data in shared section> |

| WMB |

|

|

The example above is similar to that in Section 5.5.4, except a WMB is substituted for the sec- ond MB in the

1.All data locations that are read or written in the critical section are accessed only after acquiring a software lock by using lock_variable (and before releasing the software lock).

2.For each read u of shared data in the critical section, there is a write v such that:

a.v is BEFORE the WMB

b.v follows u in processor issue sequence (see Section 5.6.1.1)

c.v either depends on u (see Section 5.6.1.7) or overlaps u (see Section 5.6.1), or both.

3.Both lock_variable and all the shared data are in

The substitution of a WMB for the second MB is usually faster and never slower.