For the Windows NT Alpha Operating System

When a counter overflows and interrupt enabling conditions are correct, the counter causes an interrupt to PALcode. The PALcode builds a frame on the kernel stack and dispatches to the kernel at the interrupt entry point.

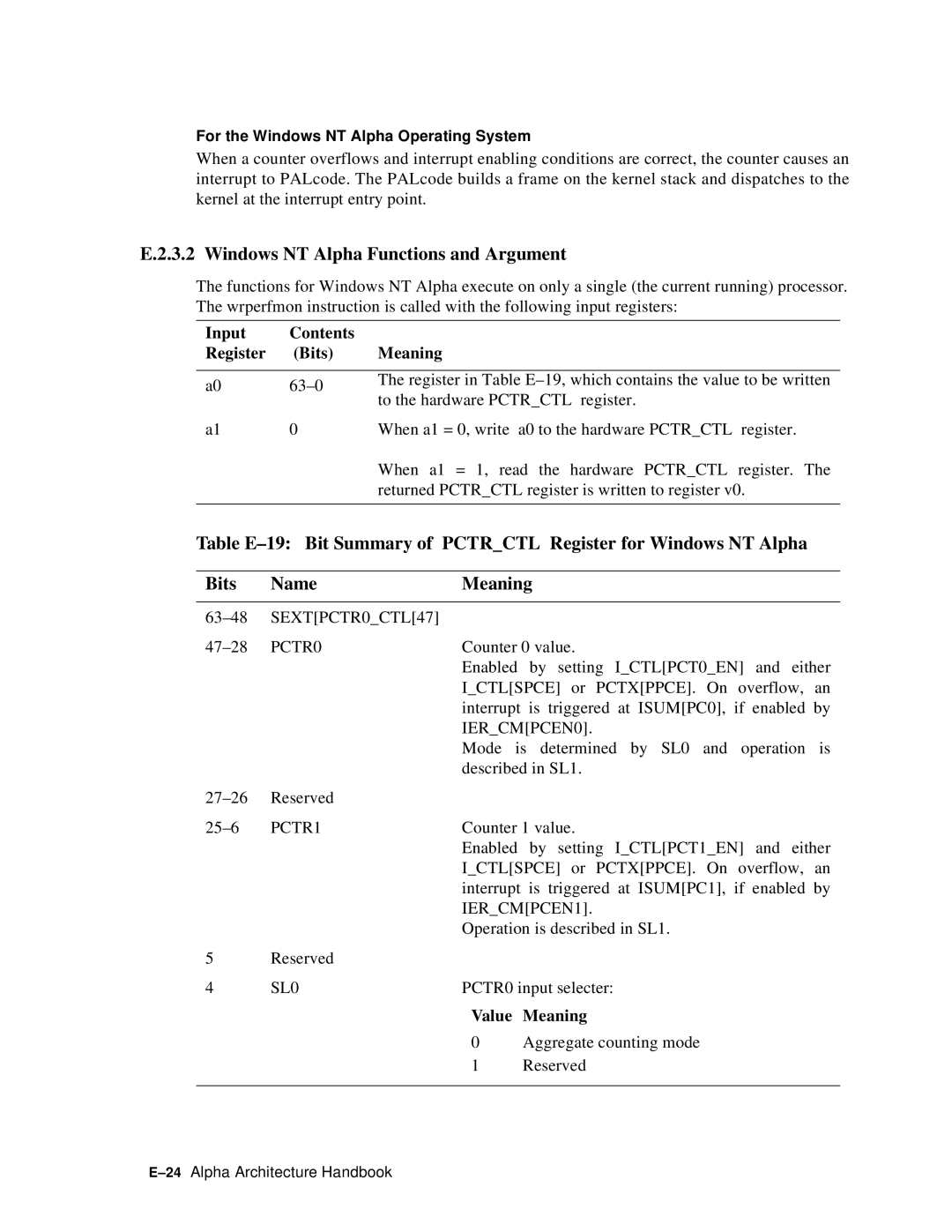

E.2.3.2 Windows NT Alpha Functions and Argument

The functions for Windows NT Alpha execute on only a single (the current running) processor. The wrperfmon instruction is called with the following input registers:

Input Contents

Register (Bits) Meaning

a063–0

a10

The register in Table

When a1 = 0, write a0 to the hardware PCTR_CTL register.

When a1 = 1, read the hardware PCTR_CTL register. The returned PCTR_CTL register is written to register v0.

Table

Bits | Name | Meaning |

|

|

|

|

|

|

|

SEXT[PCTR0_CTL[47] |

|

|

| |

PCTR0 | Counter 0 value. |

|

| |

|

| Enabled by setting I_CTL[PCT0_EN] | and | either |

|

| I_CTL[SPCE] or PCTX[PPCE]. On overflow, an | ||

|

| interrupt is triggered at ISUM[PC0], if enabled by | ||

|

| IER_CM[PCEN0]. |

|

|

|

| Mode is determined by SL0 and operation is | ||

|

| described in SL1. |

|

|

Reserved |

|

|

| |

PCTR1 | Counter 1 value. |

|

| |

|

| Enabled by setting I_CTL[PCT1_EN] | and | either |

|

| I_CTL[SPCE] or PCTX[PPCE]. On overflow, an | ||

|

| interrupt is triggered at ISUM[PC1], if enabled by | ||

|

| IER_CM[PCEN1]. |

|

|

|

| Operation is described in SL1. |

|

|

5 | Reserved |

|

|

|

4 | SL0 | PCTR0 input selecter: |

|

|

Value Meaning

0Aggregate counting mode

1Reserved