4.3 Control Instructions

Alpha provides integer conditional branch, unconditional branch, branch to subroutine, and jump instructions. The PC used in these instructions is the updated PC, as described in Section 3.1.1.

To allow implementations to achieve high performance, the Alpha architecture includes explicit hints based on a

•For many implementations of computed branches (JSR/RET/JMP), there is a substan- tial performance gain in forming a good guess of the expected target

•For many implementations, the

•Correctly predicting subroutine returns is important for good performance. Some implementations will therefore keep a small stack of predicted subroutine return

The Alpha architecture provides three kinds of

For computed branches, the otherwise unused displacement field contains a function code (JMP/JSR/RET/JSR_COROUTINE), and, for JSR and JMP, a field that statically specifies the 16 low bits of the most likely target address. The

For all branches, hint or opcode bits are used to distinguish simple branches, subroutine calls, subroutine returns, and coroutine links. These distinctions allow

For conditional branches, the sign of the target displacement is used as a

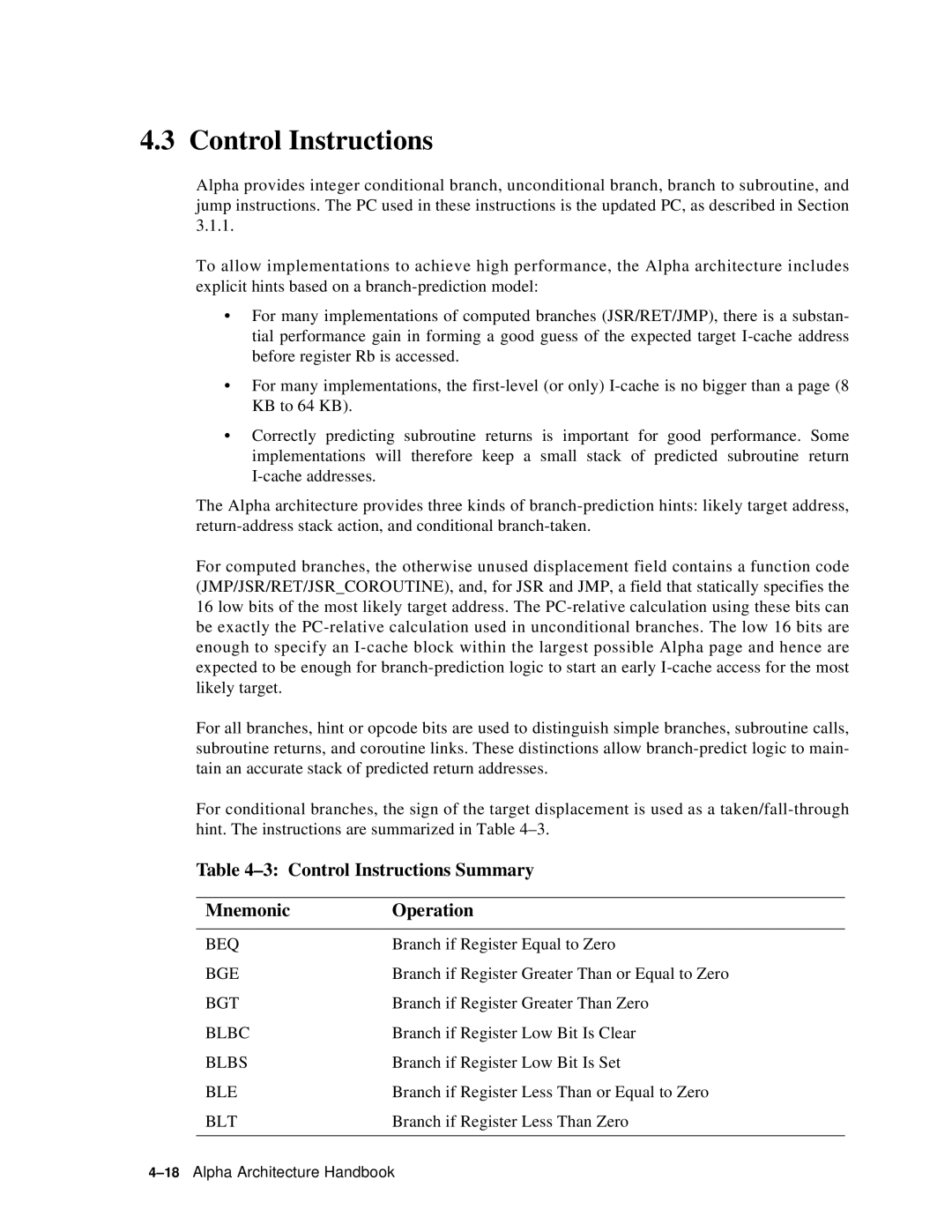

Table 4–3: Control Instructions Summary

Mnemonic | Operation |

|

|

BEQ | Branch if Register Equal to Zero |

BGE | Branch if Register Greater Than or Equal to Zero |

BGT | Branch if Register Greater Than Zero |

BLBC | Branch if Register Low Bit Is Clear |

BLBS | Branch if Register Low Bit Is Set |

BLE | Branch if Register Less Than or Equal to Zero |

BLT | Branch if Register Less Than Zero |

|

|