Description:

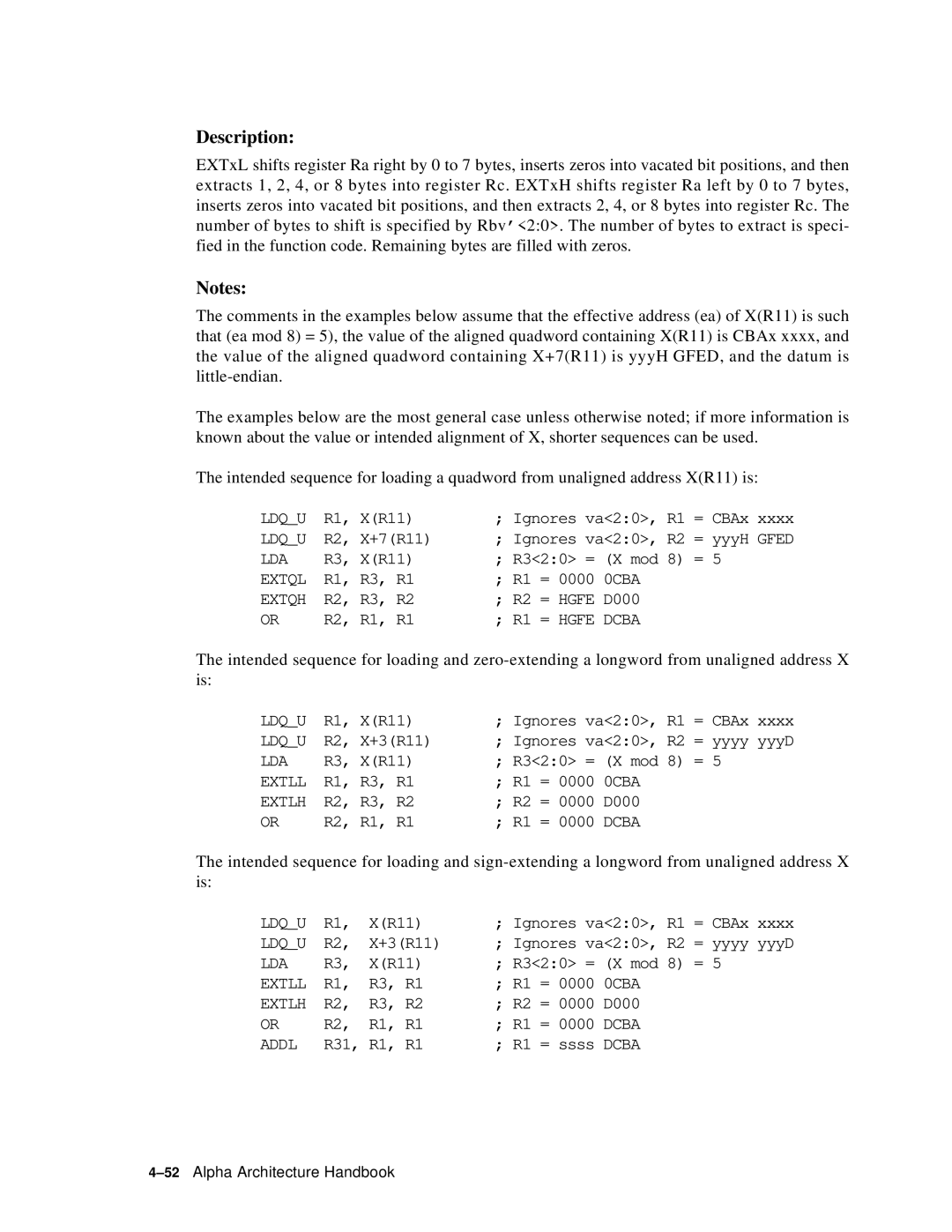

EXTxL shifts register Ra right by 0 to 7 bytes, inserts zeros into vacated bit positions, and then extracts 1, 2, 4, or 8 bytes into register Rc. EXTxH shifts register Ra left by 0 to 7 bytes, inserts zeros into vacated bit positions, and then extracts 2, 4, or 8 bytes into register Rc. The number of bytes to shift is specified by Rbv’<2:0>. The number of bytes to extract is speci- fied in the function code. Remaining bytes are filled with zeros.

Notes:

The comments in the examples below assume that the effective address (ea) of X(R11) is such that (ea mod 8) = 5), the value of the aligned quadword containing X(R11) is CBAx xxxx, and the value of the aligned quadword containing X+7(R11) is yyyH GFED, and the datum is

The examples below are the most general case unless otherwise noted; if more information is known about the value or intended alignment of X, shorter sequences can be used.

The intended sequence for loading a quadword from unaligned address X(R11) is:

LDQ_U | R1, X(R11) | ; Ignores va<2:0>, R1 = CBAx xxxx | |

LDQ_U | R2, X+7(R11) | ; Ignores va<2:0>, R2 = yyyH GFED | |

LDA | R3, X(R11) | ; R3<2:0> = (X mod 8) = 5 | |

EXTQL | R1, R3, R1 | ; R1 | = 0000 0CBA |

EXTQH | R2, R3, R2 | ; R2 | = HGFE D000 |

OR | R2, R1, R1 | ; R1 | = HGFE DCBA |

The intended sequence for loading and

LDQ_U | R1, X(R11) | ; Ignores va<2:0>, R1 = CBAx xxxx | ||

LDQ_U | R2, X+3(R11) | ; Ignores va<2:0>, R2 = yyyy yyyD | ||

LDA | R3, X(R11) | ; R3<2:0> = (X mod 8) = 5 | ||

EXTLL | R1, R3, R1 | ; R1 | = 0000 | 0CBA |

EXTLH | R2, R3, R2 | ; R2 | = 0000 | D000 |

OR | R2, R1, R1 | ; R1 | = 0000 | DCBA |

The intended sequence for loading and

LDQ_U | R1, | X(R11) | ; Ignores va<2:0>, R1 = CBAx xxxx | ||

LDQ_U | R2, | X+3(R11) | ; Ignores va<2:0>, R2 = yyyy yyyD | ||

LDA | R3, | X(R11) | ; R3<2:0> = (X mod 8) = 5 | ||

EXTLL | R1, | R3, R1 | ; R1 | = 0000 | 0CBA |

EXTLH | R2, | R3, R2 | ; R2 | = 0000 | D000 |

OR | R2, | R1, R1 | ; R1 | = 0000 | DCBA |

ADDL | R31, | R1, R1 | ; R1 | = ssss DCBA | |