4.3.1 Conditional Branch

Format:

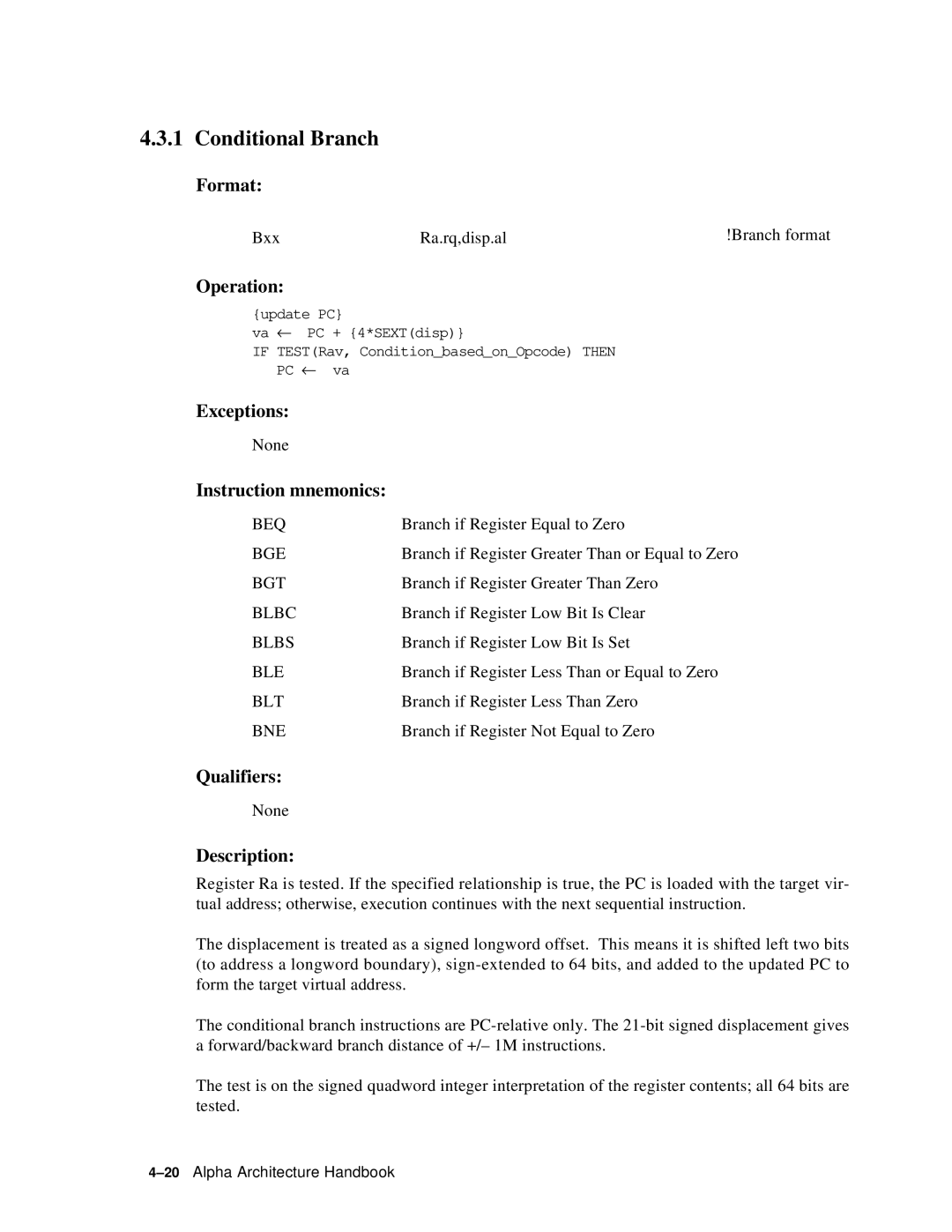

Bxx | Ra.rq,disp.al | !Branch format |

Operation:

{update PC}

va ← PC + {4*SEXT(disp)}

IF TEST(Rav, Condition_based_on_Opcode) THEN PC ← va

Exceptions: |

|

None |

|

Instruction mnemonics: |

|

BEQ | Branch if Register Equal to Zero |

BGE | Branch if Register Greater Than or Equal to Zero |

BGT | Branch if Register Greater Than Zero |

BLBC | Branch if Register Low Bit Is Clear |

BLBS | Branch if Register Low Bit Is Set |

BLE | Branch if Register Less Than or Equal to Zero |

BLT | Branch if Register Less Than Zero |

BNE | Branch if Register Not Equal to Zero |

Qualifiers: |

|

None |

|

Description:

Register Ra is tested. If the specified relationship is true, the PC is loaded with the target vir- tual address; otherwise, execution continues with the next sequential instruction.

The displacement is treated as a signed longword offset. This means it is shifted left two bits (to address a longword boundary),

The conditional branch instructions are

The test is on the signed quadword integer interpretation of the register contents; all 64 bits are tested.