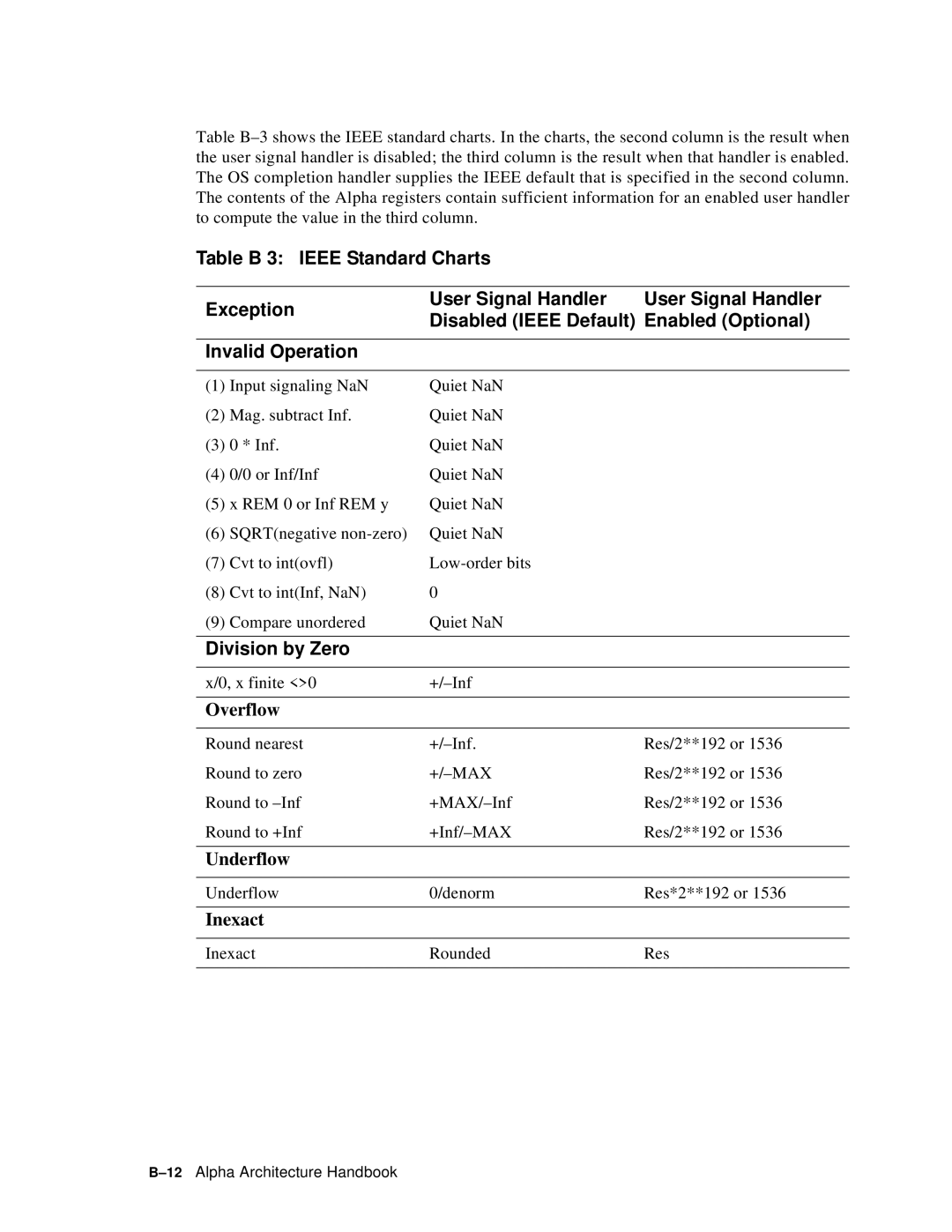

Table

Table

Exception | User Signal Handler | User Signal Handler | ||

Disabled (IEEE Default) | Enabled (Optional) | |||

|

| |||

|

|

| ||

Invalid Operation |

|

| ||

|

|

|

| |

(1) | Input signaling NaN | Quiet NaN |

| |

(2) | Mag. subtract Inf. | Quiet NaN |

| |

(3) | 0 * Inf. | Quiet NaN |

| |

(4) | 0/0 or Inf/Inf | Quiet NaN |

| |

(5) x REM 0 or Inf REM y | Quiet NaN |

| ||

(6) | SQRT(negative | Quiet NaN |

| |

(7) | Cvt to int(ovfl) |

| ||

(8) | Cvt to int(Inf, NaN) | 0 |

| |

(9) | Compare unordered | Quiet NaN |

| |

|

|

| ||

Division by Zero |

|

| ||

|

|

| ||

x/0, x finite <>0 |

| |||

|

|

| ||

Overflow |

|

| ||

|

|

| ||

Round nearest | Res /2**192 or 1536 | |||

Round to zero | Res/2**192 or 1536 | |||

Round to | Res/2**192 or 1536 | |||

Round to +Inf | Res/2**192 or 1536 | |||

|

|

| ||

Underflow |

|

| ||

|

|

| ||

Underflow | 0/denorm | Res*2**192 or 1536 | ||

|

|

| ||

Inexact |

|

| ||

|

|

| ||

Inexact | Rounded | Res | ||

|

|

|

| |