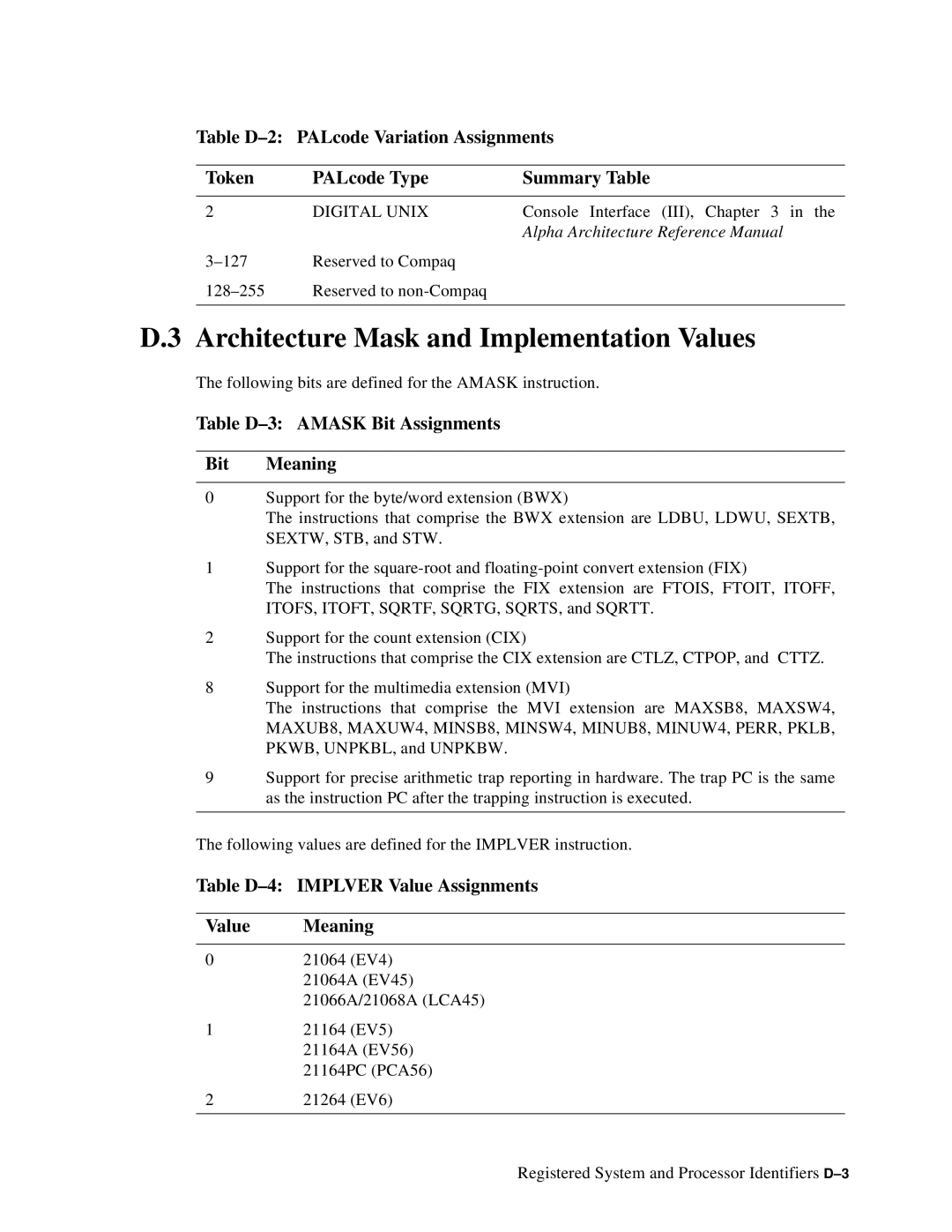

Table

Token | PALcode Type | Summary Table |

|

|

|

2 | DIGITAL UNIX | Console Interface (III), Chapter 3 in the |

|

| Alpha Architecture Reference Manual |

Reserved to Compaq |

| |

Reserved to |

| |

|

|

|

D.3 Architecture Mask and Implementation Values

The following bits are defined for the AMASK instruction.

Table D–3: AMASK Bit Assignments

Bit Meaning

0Support for the byte/word extension (BWX)

The instructions that comprise the BWX extension are LDBU, LDWU, SEXTB, SEXTW, STB, and STW.

1Support for the

The instructions that comprise the FIX extension are FTOIS, FTOIT, ITOFF, ITOFS, ITOFT, SQRTF, SQRTG, SQRTS, and SQRTT.

2Support for the count extension (CIX)

The instructions that comprise the CIX extension are CTLZ, CTPOP, and CTTZ.

8Support for the multimedia extension (MVI)

The instructions that comprise the MVI extension are MAXSB8, MAXSW4, MAXUB8, MAXUW4, MINSB8, MINSW4, MINUB8, MINUW4, PERR, PKLB, PKWB, UNPKBL, and UNPKBW.

9Support for precise arithmetic trap reporting in hardware. The trap PC is the same as the instruction PC after the trapping instruction is executed.

The following values are defined for the IMPLVER instruction.

Table D–4: IMPLVER Value Assignments

Value | Meaning |

|

|

0 | 21064 (EV4) |

| 21064A (EV45) |

| 21066A/21068A (LCA45) |

1 | 21164 (EV5) |

| 21164A (EV56) |

| 21164PC (PCA56) |

2 | 21264 (EV6) |

|

|

Registered System and Processor Identifiers