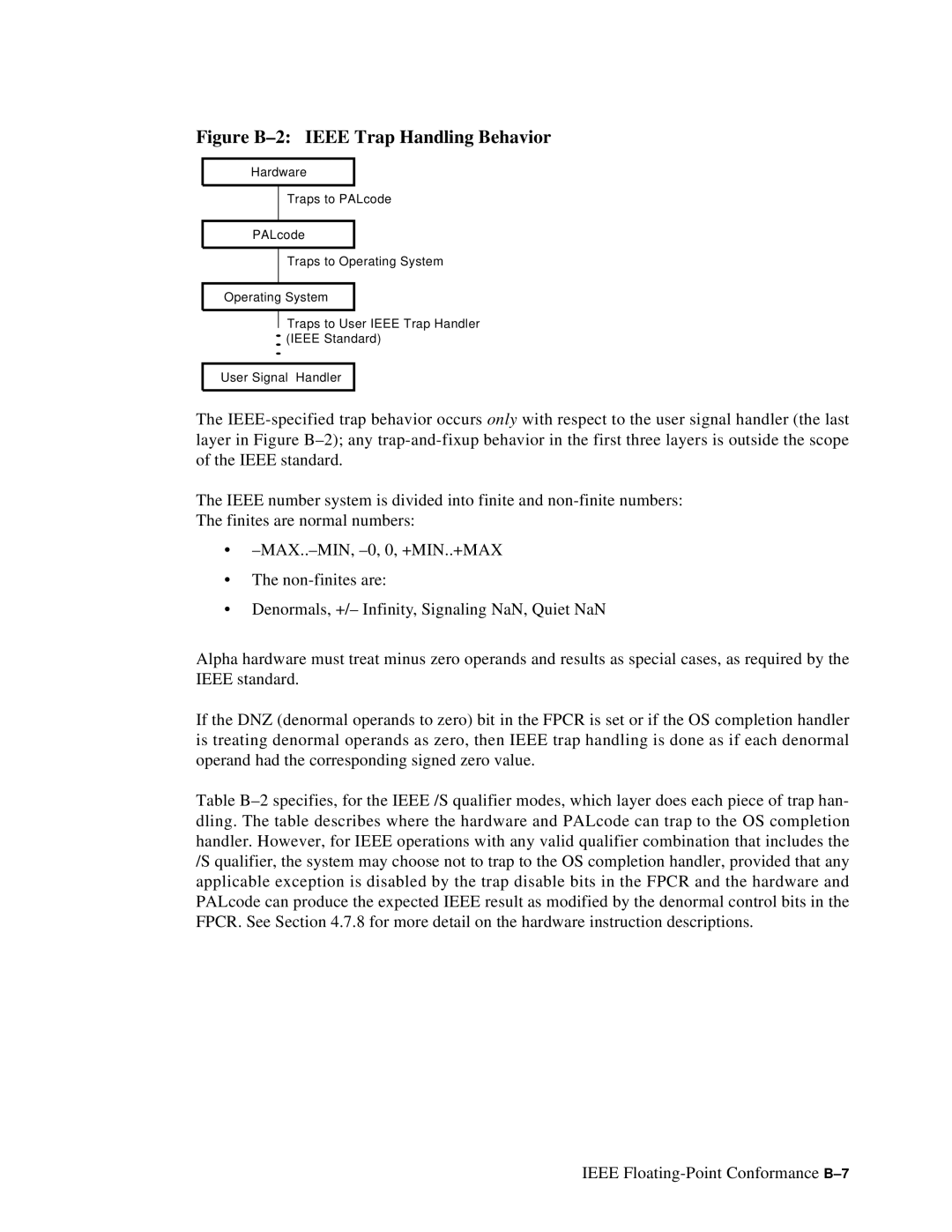

Figure B–2: IEEE Trap Handling Behavior

Hardware

Traps to PALcode

PALcode

Traps to Operating System

Operating System

Traps to User IEEE Trap Handler

![]() (IEEE Standard)

(IEEE Standard)

User Signal Handler

The

The IEEE number system is divided into finite and

The finites are normal numbers:

•

•The

•Denormals, +/– Infinity, Signaling NaN, Quiet NaN

Alpha hardware must treat minus zero operands and results as special cases, as required by the IEEE standard.

If the DNZ (denormal operands to zero) bit in the FPCR is set or if the OS completion handler is treating denormal operands as zero, then IEEE trap handling is done as if each denormal operand had the corresponding signed zero value.

Table

IEEE