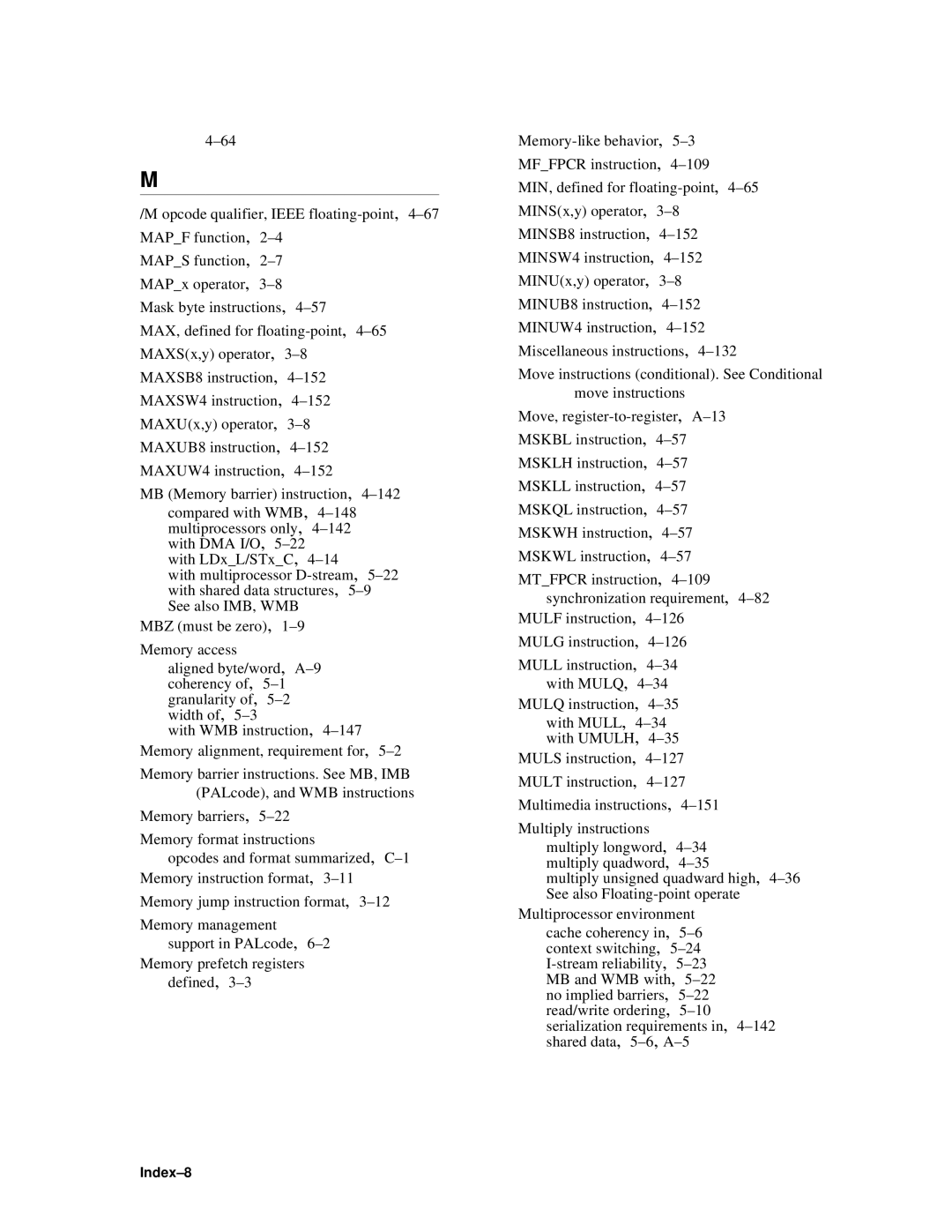

M

/M opcode qualifier, IEEE

MAP_S function,

MAX, defined for

MB (Memory barrier) instruction,

compared with WMB,

with LDx_L/STx_C,

with multiprocessor

MBZ (must be zero),

Memory access

aligned byte/word,

with WMB instruction,

Memory barrier instructions. See MB, IMB (PALcode), and WMB instructions

Memory barriers,

Memory format instructions

opcodes and format summarized,

Memory jump instruction format,

Memory management support in PALcode,

Memory prefetch registers defined,

MINSB8 instruction,

Move instructions (conditional). See Conditional move instructions

Move,

MT_FPCR instruction,

MULF instruction,

MULG instruction,

MULL instruction,

MULQ instruction,

with MULL,

MULS instruction,

MULT instruction,

Multimedia instructions,

Multiply instructions

multiply longword,

multiply unsigned quadward high,

Multiprocessor environment

cache coherency in,