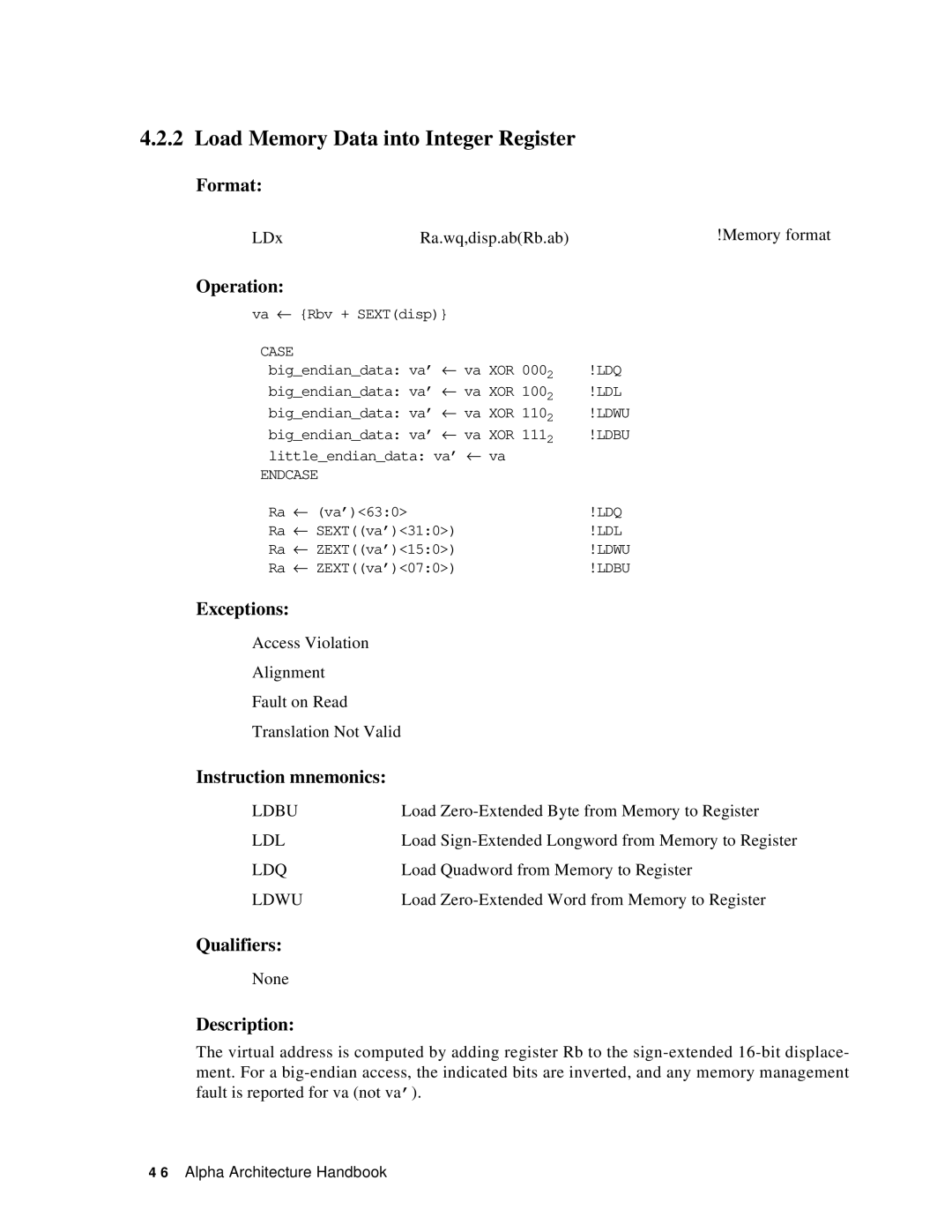

4.2.2 Load Memory Data into Integer Register

Format:

LDxRa.wq,disp.ab(Rb.ab)!Memory format

Operation:

va ← {Rbv + SEXT(disp)} |

|

CASE |

|

big_endian_data: va’ ← va XOR 0002 | !LDQ |

big_endian_data: va’ ← va XOR 1002 | !LDL |

big_endian_data: va’ ← va XOR 1102 | !LDWU |

big_endian_data: va’ ← va XOR 1112 | !LDBU |

little_endian_data: va’ ← va |

|

ENDCASE |

|

Ra ← (va’)<63:0> | !LDQ |

Ra ← SEXT((va’)<31:0>) | !LDL |

Ra ← ZEXT((va’)<15:0>) | !LDWU |

Ra ← ZEXT((va’)<07:0>) | !LDBU |

Exceptions:

Access Violation

Alignment

Fault on Read

Translation Not Valid

Instruction mnemonics:

LDBU | Load |

LDL | Load |

LDQ | Load Quadword from Memory to Register |

LDWU | Load |

Qualifiers:

None

Description:

The virtual address is computed by adding register Rb to the