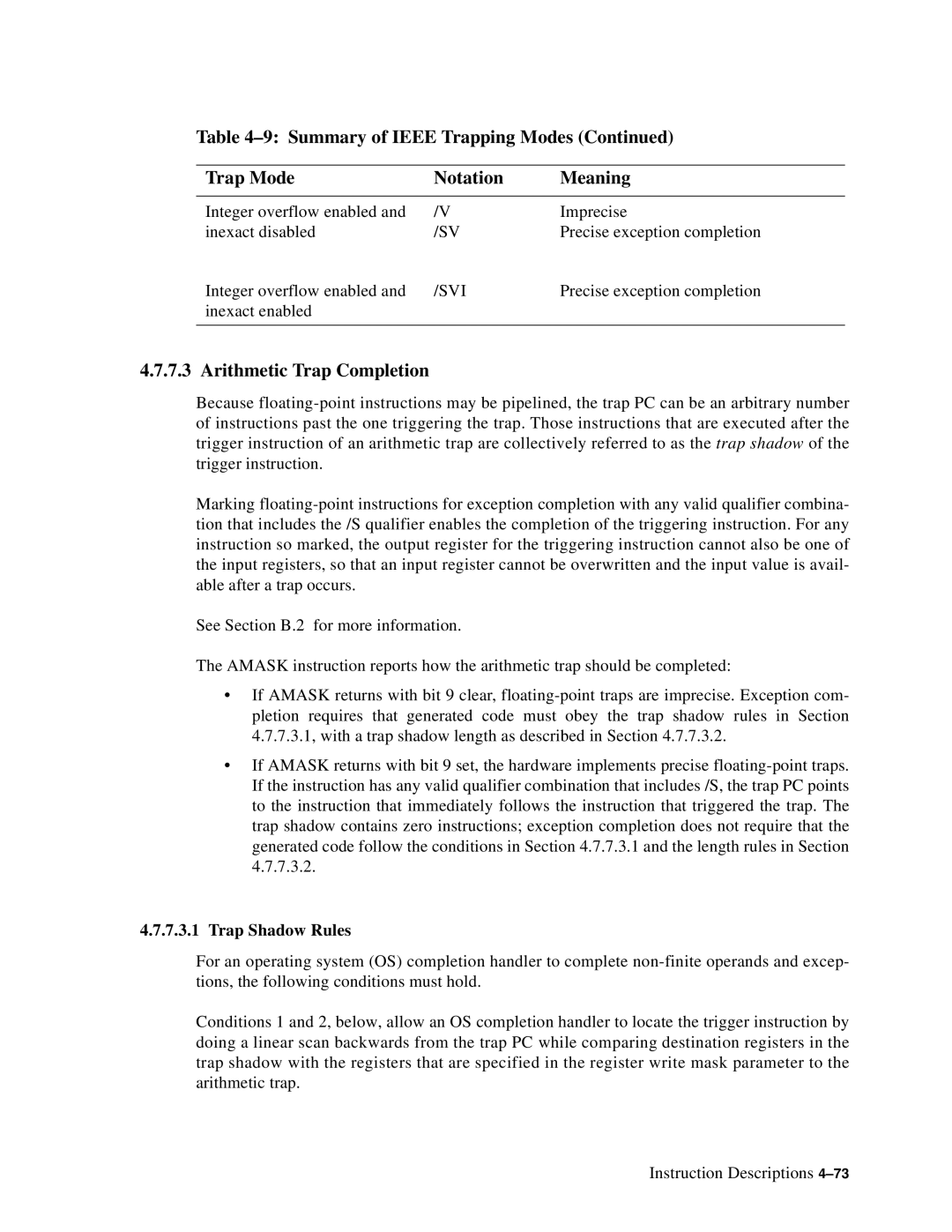

Table 4–9: Summary of IEEE Trapping Modes (Continued)

Trap Mode | Notation | Meaning |

|

|

|

Integer overflow enabled and | /V | Imprecise |

inexact disabled | /SV | Precise exception completion |

Integer overflow enabled and | /SVI | Precise exception completion |

inexact enabled |

|

|

|

|

|

4.7.7.3 Arithmetic Trap Completion

Because

Marking

See Section B.2 for more information.

The AMASK instruction reports how the arithmetic trap should be completed:

•If AMASK returns with bit 9 clear,

•If AMASK returns with bit 9 set, the hardware implements precise

4.7.7.3.1Trap Shadow Rules

For an operating system (OS) completion handler to complete

Conditions 1 and 2, below, allow an OS completion handler to locate the trigger instruction by doing a linear scan backwards from the trap PC while comparing destination registers in the trap shadow with the registers that are specified in the register write mask parameter to the arithmetic trap.

Instruction Descriptions