•Integer overflow (IOV) exceptions are controlled by the INVE enable mask bit (FP_C<1>), as allowed by the IEEE standard. Implementation software is responsible for setting the INVS status bit (FP_C<17>) when a CVTTQ or CVTQL instruction traps into the software completion mechanism for integer overflow .

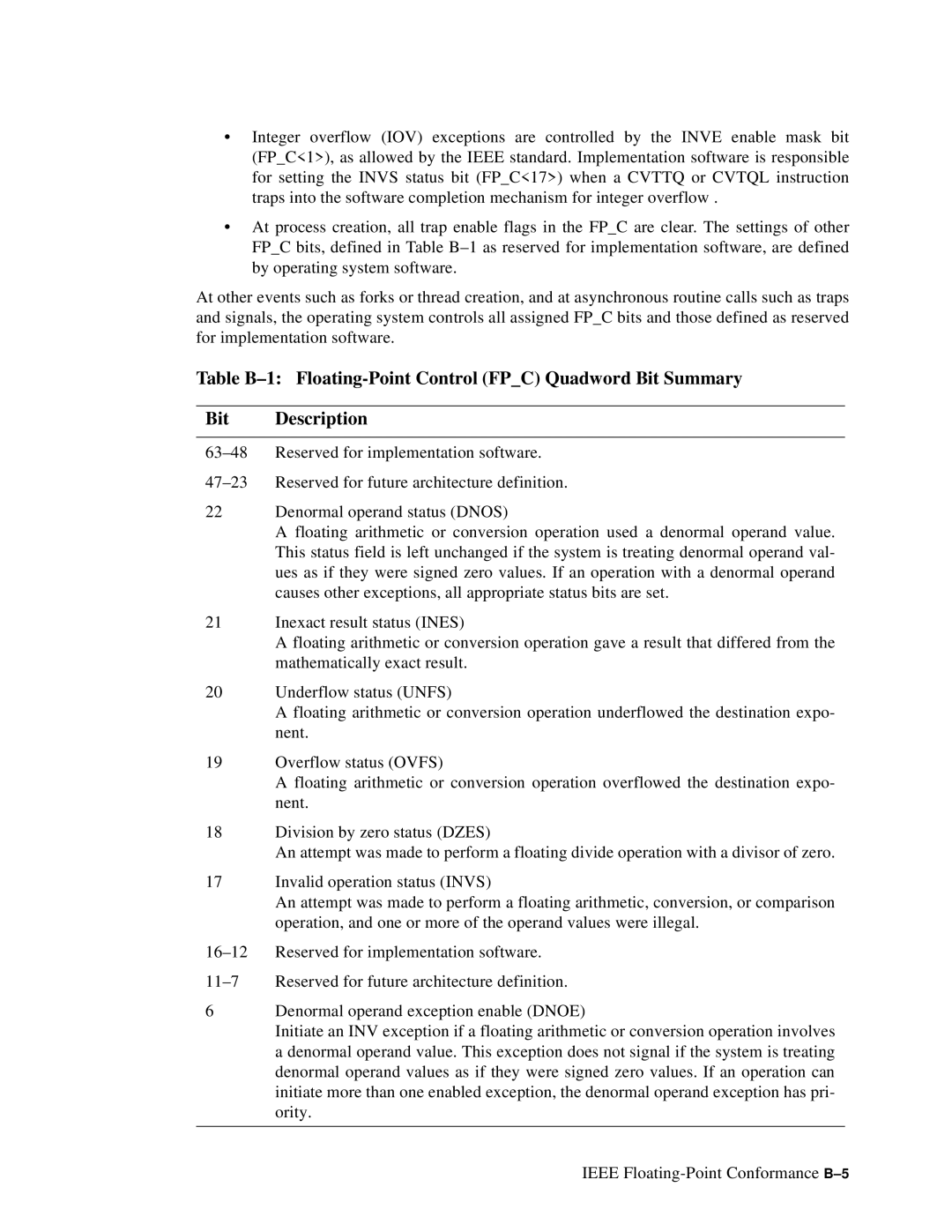

•At process creation, all trap enable flags in the FP_C are clear. The settings of other FP_C bits, defined in Table

At other events such as forks or thread creation, and at asynchronous routine calls such as traps and signals, the operating system controls all assigned FP_C bits and those defined as reserved for implementation software.

Table

Bit Description

22Denormal operand status (DNOS)

A floating arithmetic or conversion operation used a denormal operand value. This status field is left unchanged if the system is treating denormal operand val- ues as if they were signed zero values. If an operation with a denormal operand causes other exceptions, all appropriate status bits are set.

21Inexact result status (INES)

A floating arithmetic or conversion operation gave a result that differed from the mathematically exact result.

20Underflow status (UNFS)

A floating arithmetic or conversion operation underflowed the destination expo- nent.

19Overflow status (OVFS)

A floating arithmetic or conversion operation overflowed the destination expo- nent.

18Division by zero status (DZES)

An attempt was made to perform a floating divide operation with a divisor of zero.

17Invalid operation status (INVS)

An attempt was made to perform a floating arithmetic, conversion, or comparison operation, and one or more of the operand values were illegal.

6Denormal operand exception enable (DNOE)

Initiate an INV exception if a floating arithmetic or conversion operation involves a denormal operand value. This exception does not signal if the system is treating denormal operand values as if they were signed zero values. If an operation can initiate more than one enabled exception, the denormal operand exception has pri- ority.

IEEE