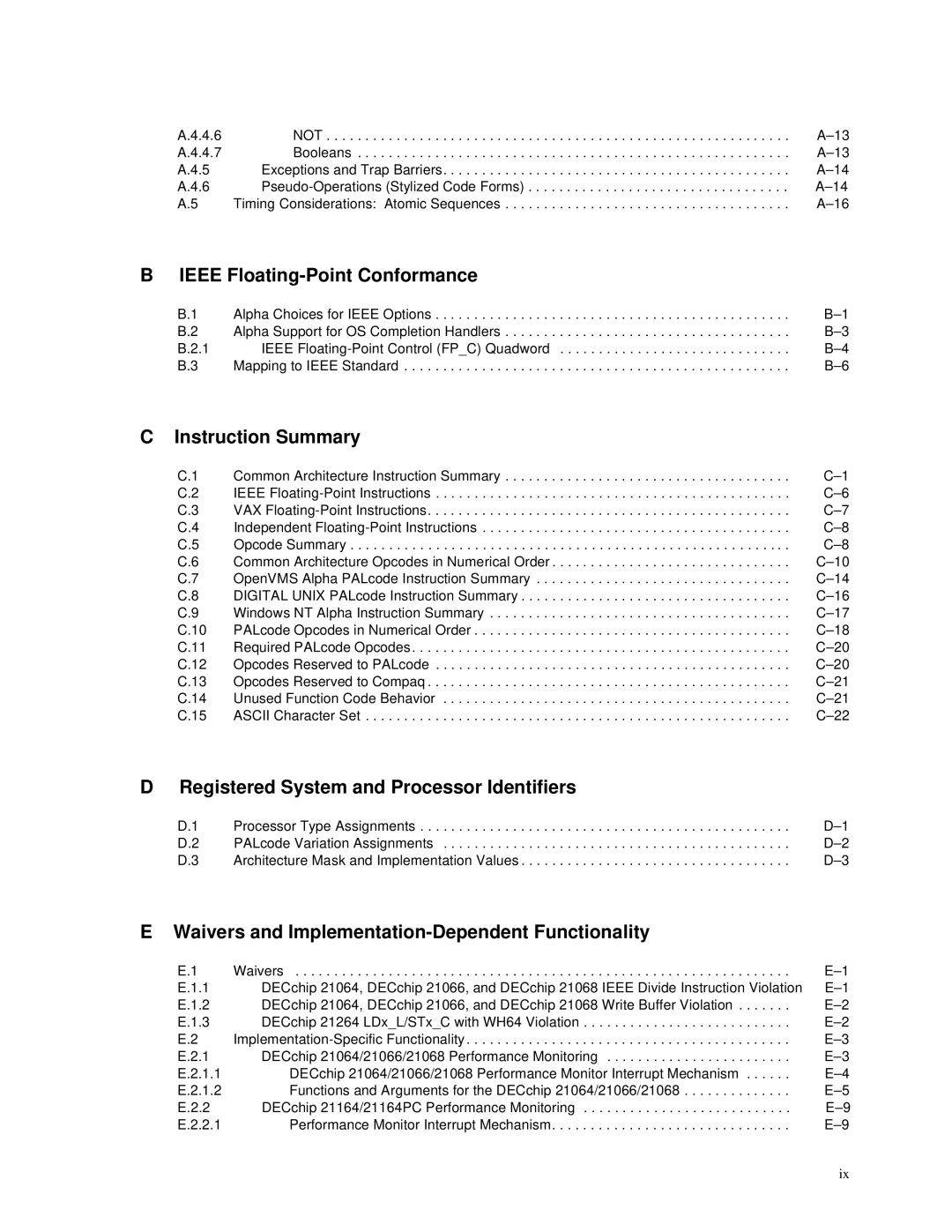

A.4.4.6 | NOT | |

A.4.4.7 | Booleans | |

A.4.5 | Exceptions and Trap Barriers | |

A.4.6 | ||

A.5 | Timing Considerations: Atomic Sequences |

B IEEE Floating-Point Conformance

| B.1 | Alpha Choices for IEEE Options | |

| B.2 | Alpha Support for OS Completion Handlers | |

| B.2.1 | IEEE | |

| B.3 | Mapping to IEEE Standard | |

C | Instruction Summary |

| |

| C.1 | Common Architecture Instruction Summary | |

| C.2 | IEEE | |

| C.3 | VAX | |

| C.4 | Independent | |

| C.5 | Opcode Summary | |

| C.6 | Common Architecture Opcodes in Numerical Order | |

| C.7 | OpenVMS Alpha PALcode Instruction Summary | |

| C.8 | DIGITAL UNIX PALcode Instruction Summary | |

| C.9 | Windows NT Alpha Instruction Summary | |

| C.10 | PALcode Opcodes in Numerical Order | |

| C.11 | Required PALcode Opcodes | |

| C.12 | Opcodes Reserved to PALcode | |

| C.13 | Opcodes Reserved to Compaq | |

| C.14 | Unused Function Code Behavior | |

| C.15 | ASCII Character Set | |

D | Registered System and Processor Identifiers |

| |

| D.1 | Processor Type Assignments | |

| D.2 | PALcode Variation Assignments | |

| D.3 | Architecture Mask and Implementation Values | |

E Waivers and Implementation-Dependent Functionality

E.1 | Waivers | |

E.1.1 | DECchip 21064, DECchip 21066, and DECchip 21068 IEEE Divide Instruction Violation | |

E.1.2 | DECchip 21064, DECchip 21066, and DECchip 21068 Write Buffer Violation | |

E.1.3 | DECchip 21264 LDx_L/STx_C with WH64 Violation | |

E.2 | ||

E.2.1 | DECchip 21064/21066/21068 Performance Monitoring | |

E.2.1.1 | DECchip 21064/21066/21068 Performance Monitor Interrupt Mechanism | |

E.2.1.2 | Functions and Arguments for the DECchip 21064/21066/21068 | |

E.2.2 | DECchip 21164/21164PC Performance Monitoring | |

E.2.2.1 | Performance Monitor Interrupt Mechanism |

ix