This implies that after a DMA I/O device has written some

ing in a page from disk), the DMA device must logically execute an MB1 before posting a completion interrupt, and the interrupt handler software must execute a CALL_PAL IMB before the

An important special case occurs under the following circumstances:

1.A write (perhaps by an I/O device) is done to some physical page frame.

2.A CALL_PAL IMB (or MB) is executed.

3.A previously invalid PTE is changed to be a valid mapping of the physical page frame that was written in step 1.

In this case, all processors that access virtual memory by using the newly valid PTE must guar- antee to deliver the newly written

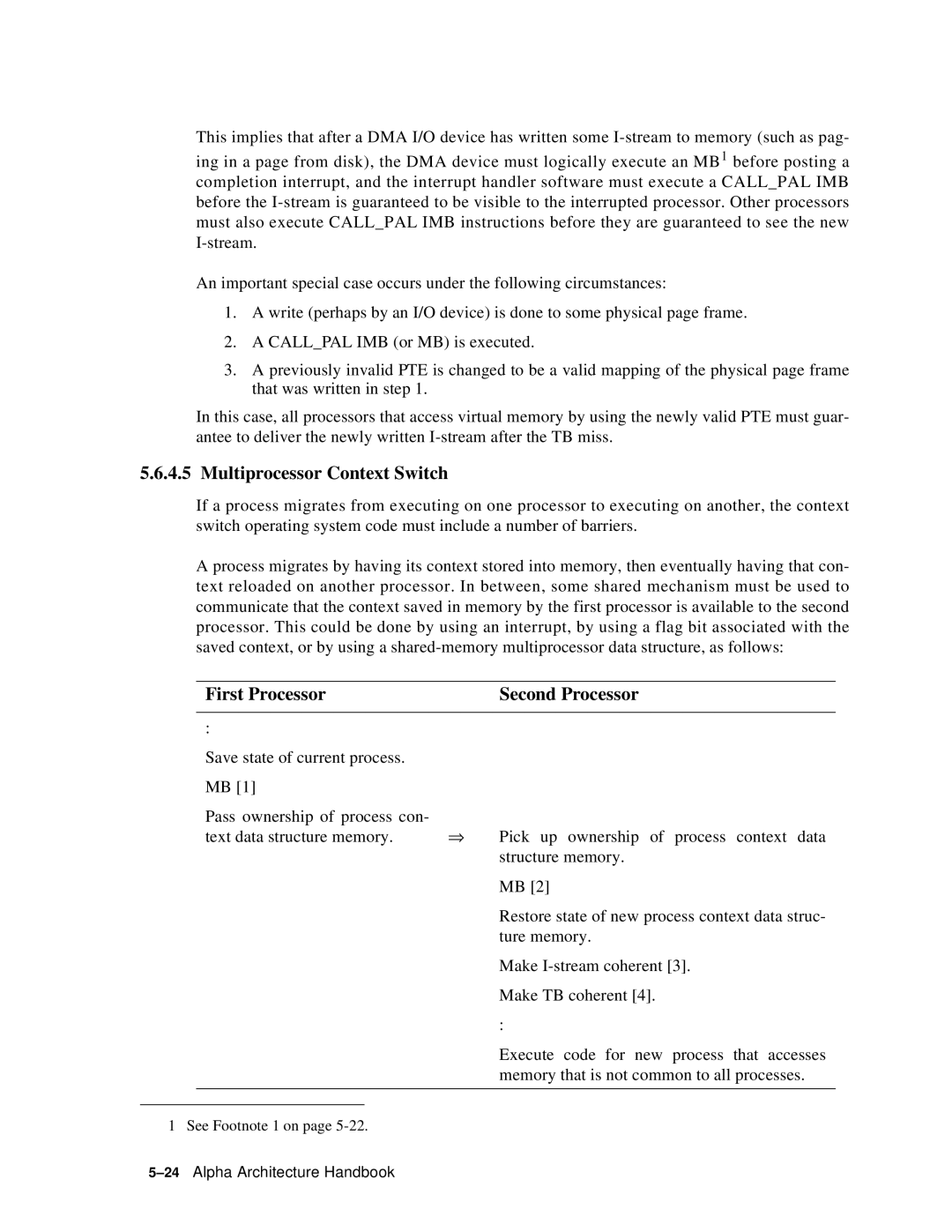

5.6.4.5 Multiprocessor Context Switch

If a process migrates from executing on one processor to executing on another, the context switch operating system code must include a number of barriers.

A process migrates by having its context stored into memory, then eventually having that con- text reloaded on another processor. In between, some shared mechanism must be used to communicate that the context saved in memory by the first processor is available to the second processor. This could be done by using an interrupt, by using a flag bit associated with the saved context, or by using a

| First Processor |

| Second Processor | |

|

|

|

|

|

| : |

|

|

|

| Save state of current process. |

|

| |

| MB [1] |

|

| |

| Pass ownership of process con- | ⇒ |

| |

| text data structure memory. | Pick up ownership of process context data | ||

|

|

|

| structure memory. |

|

|

|

| MB [2] |

|

|

|

| Restore state of new process context data struc- |

|

|

|

| ture memory. |

|

|

|

| Make |

|

|

|

| Make TB coherent [4]. |

|

|

|

| : |

|

|

|

| Execute code for new process that accesses |

|

|

|

| memory that is not common to all processes. |

|

|

|

|

|

|

|

|

|

|