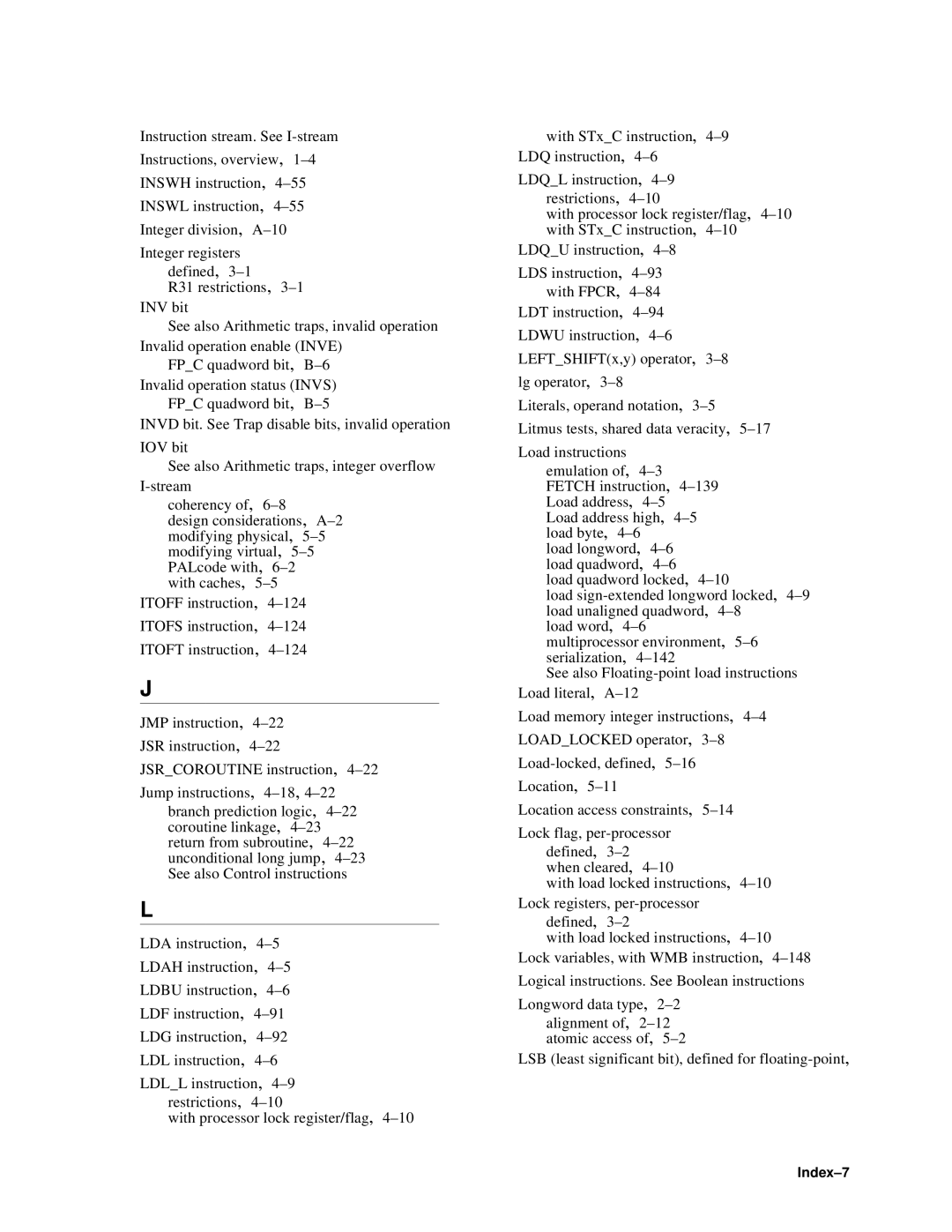

Instruction stream. See

Instructions, overview,

INSWH instruction,

INSWL instruction,

Integer division,

Integer registers

defined,

R31 restrictions,

See also Arithmetic traps, invalid operation Invalid operation enable (INVE)

FP_C quadword bit,

FP_C quadword bit,

INVD bit. See Trap disable bits, invalid operation

IOV bit

See also Arithmetic traps, integer overflow

coherency of,

design considerations,

with caches,

ITOFF instruction,

J

JMP instruction,

JSR instruction,

JSR_COROUTINE instruction,

Jump instructions,

branch prediction logic,

L

LDA instruction,

LDL_L instruction,

restrictions,

with processor lock register/flag,

with STx_C instruction,

LDQ_L instruction,

restrictions,

with processor lock register/flag,

LDQ_U instruction,

LDS instruction,

LDWU instruction,

LEFT_SHIFT(x,y) operator,

Literals, operand notation,

Litmus tests, shared data veracity,

Load instructions

emulation of,

FETCH instruction,

Load address high,

load longword,

load quadword locked,

load

load word,

multiprocessor environment,

See also

Load memory integer instructions,

LOAD_LOCKED operator,

Location,

Location access constraints,

Lock flag,

defined,

when cleared,

with load locked instructions,

defined,

with load locked instructions,

Logical instructions. See Boolean instructions

Longword data type,

alignment of,

LSB (least significant bit), defined for