A.4.5 Exceptions and Trap Barriers

The EXCB instruction allows software to guarantee that in a pipelined implementation, all pre- vious instructions have completed any behavior that is related to exceptions or rounding modes before any instructions after the EXCB are issued. In particular, all changes to the float-

The TRAPB instruction guarantees that it and any following instructions do not issue until all possible preceding traps have been signaled. This does not mean that all preceding instructions have necessarily run to completion (for example, a Load instruction may have passed all the fault checks but not yet delivered data from a cache miss).

EXCB is thus a superset of TRAPB.

A.4.6 Pseudo-Operations (Stylized Code Forms)

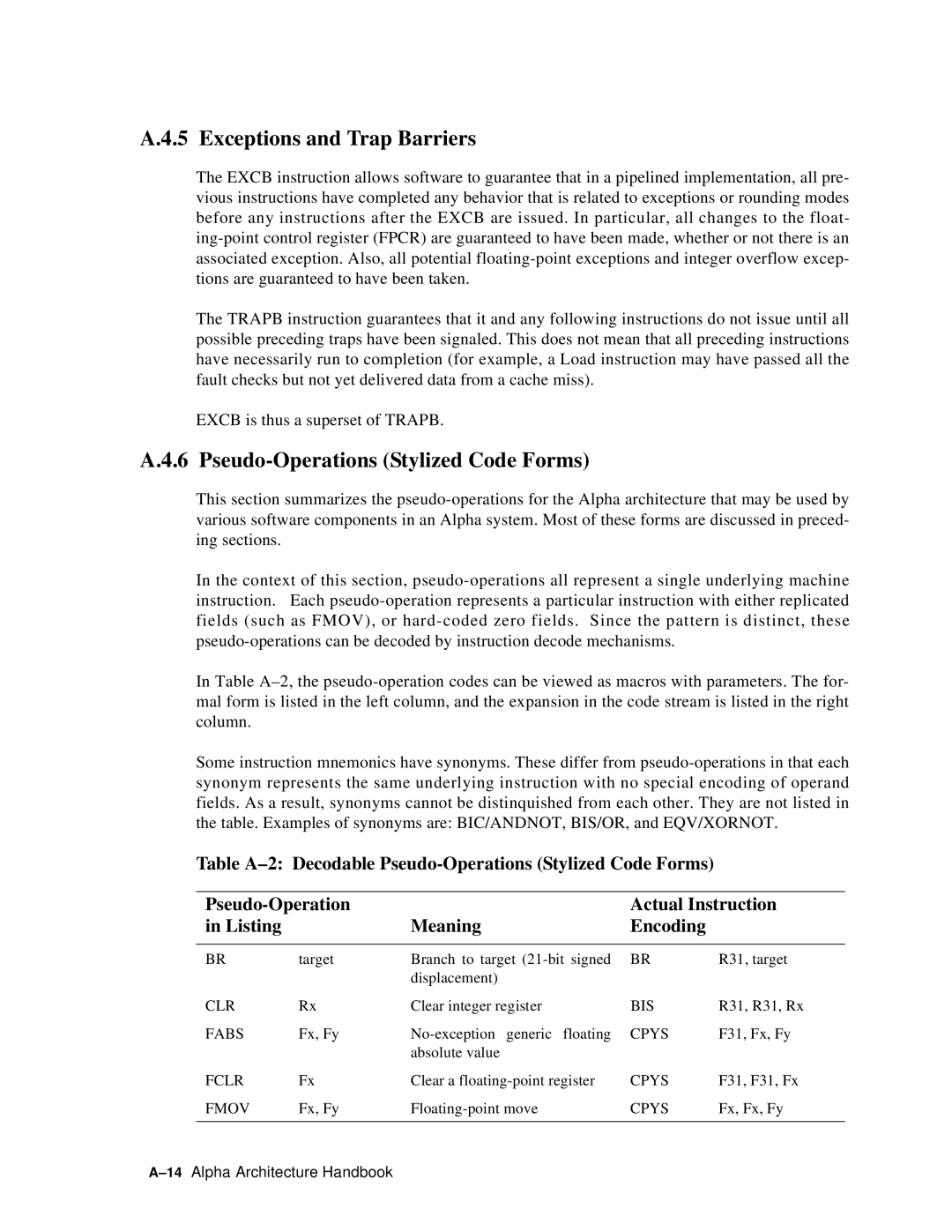

This section summarizes the

In the context of this section,

In Table

Some instruction mnemonics have synonyms. These differ from

Table

| Actual Instruction | |||

in Listing |

| Meaning | Encoding |

|

|

|

|

|

|

BR | target | Branch to target | BR | R31, target |

|

| displacement) |

|

|

CLR | Rx | Clear integer register | BIS | R31, R31, Rx |

FABS | Fx, Fy | CPYS | F31, Fx, Fy | |

|

| absolute value |

|

|

FCLR | Fx | Clear a | CPYS | F31, F31, Fx |

FMOV | Fx, Fy | CPYS | Fx, Fx, Fy | |

|

|

|

|

|