www.ti.com

SRIO Registers

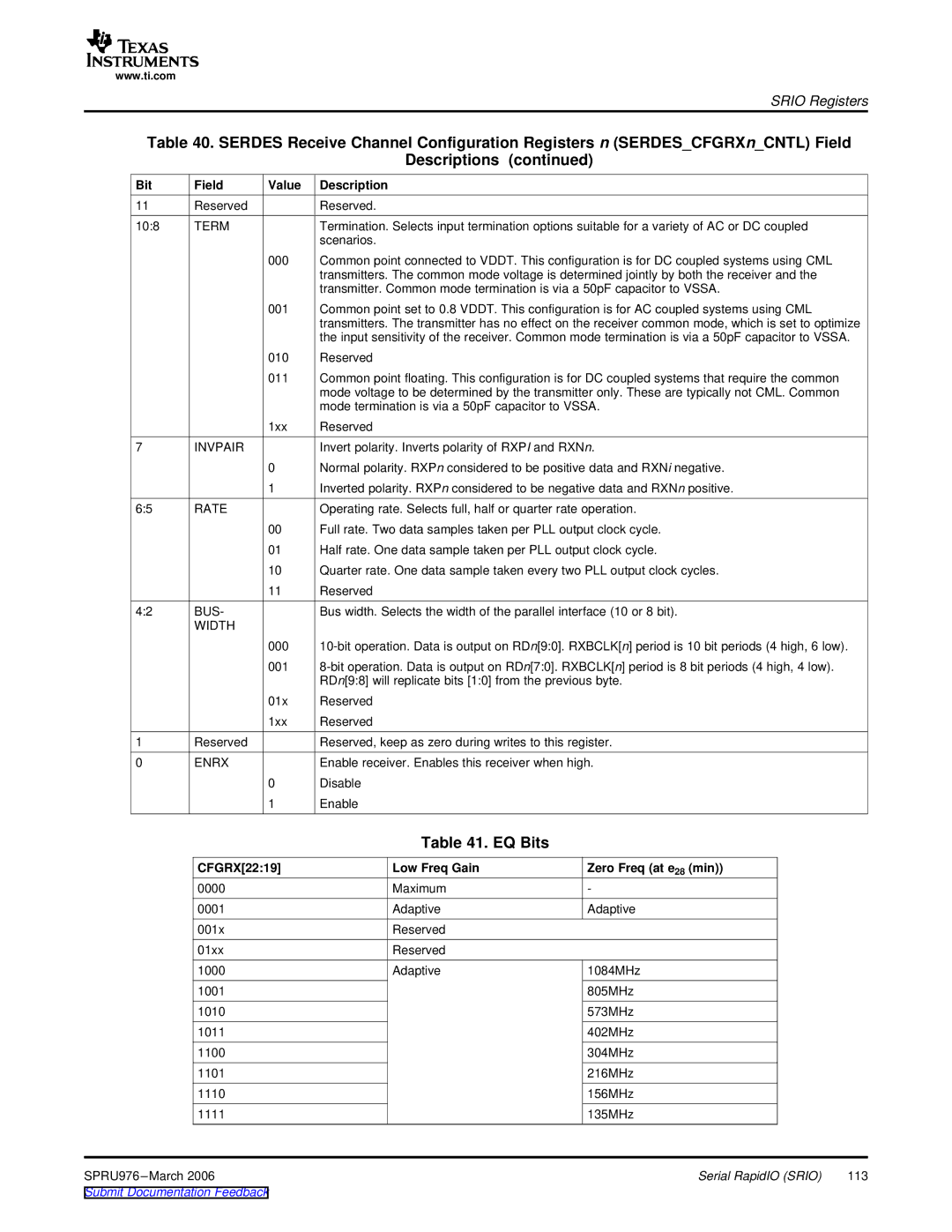

Table 40. SERDES Receive Channel Configuration Registers n (SERDES_CFGRXn_CNTL) Field

Descriptions (continued)

Bit | Field | Value | Description |

11 | Reserved |

| Reserved. |

10:8 | TERM |

| Termination. Selects input termination options suitable for a variety of AC or DC coupled |

|

|

| scenarios. |

|

| 000 | Common point connected to VDDT. This configuration is for DC coupled systems using CML |

|

|

| transmitters. The common mode voltage is determined jointly by both the receiver and the |

|

|

| transmitter. Common mode termination is via a 50pF capacitor to VSSA. |

001Common point set to 0.8 VDDT. This configuration is for AC coupled systems using CML transmitters. The transmitter has no effect on the receiver common mode, which is set to optimize the input sensitivity of the receiver. Common mode termination is via a 50pF capacitor to VSSA.

| 010 | Reserved |

| 011 | Common point floating. This configuration is for DC coupled systems that require the common |

|

| mode voltage to be determined by the transmitter only. These are typically not CML. Common |

|

| mode termination is via a 50pF capacitor to VSSA. |

| 1xx | Reserved |

7 | INVPAIR | Invert polarity. Inverts polarity of RXPI and RXNn. |

| 0 | Normal polarity. RXPn considered to be positive data and RXNi negative. |

| 1 | Inverted polarity. RXPn considered to be negative data and RXNn positive. |

6:5 | RATE | Operating rate. Selects full, half or quarter rate operation. |

| 00 | Full rate. Two data samples taken per PLL output clock cycle. |

| 01 | Half rate. One data sample taken per PLL output clock cycle. |

| 10 | Quarter rate. One data sample taken every two PLL output clock cycles. |

| 11 | Reserved |

4:2 | BUS- | Bus width. Selects the width of the parallel interface (10 or 8 bit). |

| WIDTH |

|

| 000 | |

| 001 | |

|

| RDn[9:8] will replicate bits [1:0] from the previous byte. |

| 01x | Reserved |

| 1xx | Reserved |

1 | Reserved | Reserved, keep as zero during writes to this register. |

0 | ENRX | Enable receiver. Enables this receiver when high. |

| 0 | Disable |

| 1 | Enable |

Table 41. EQ Bits

CFGRX[22:19] | Low Freq Gain | Zero Freq (at e28 (min)) |

|

0000 | Maximum | - |

|

0001 | Adaptive | Adaptive |

|

001x | Reserved |

|

|

01xx | Reserved |

|

|

1000 | Adaptive | 1084MHz |

|

1001 |

| 805MHz |

|

1010 |

| 573MHz |

|

1011 |

| 402MHz |

|

1100 |

| 304MHz |

|

1101 |

| 216MHz |

|

1110 |

| 156MHz |

|

1111 |

| 135MHz |

|

SPRU976 |

| Serial RapidIO (SRIO) | 113 |

Submit Documentation Feedback |

|

|

|