www.ti.com

Interrupt Conditions

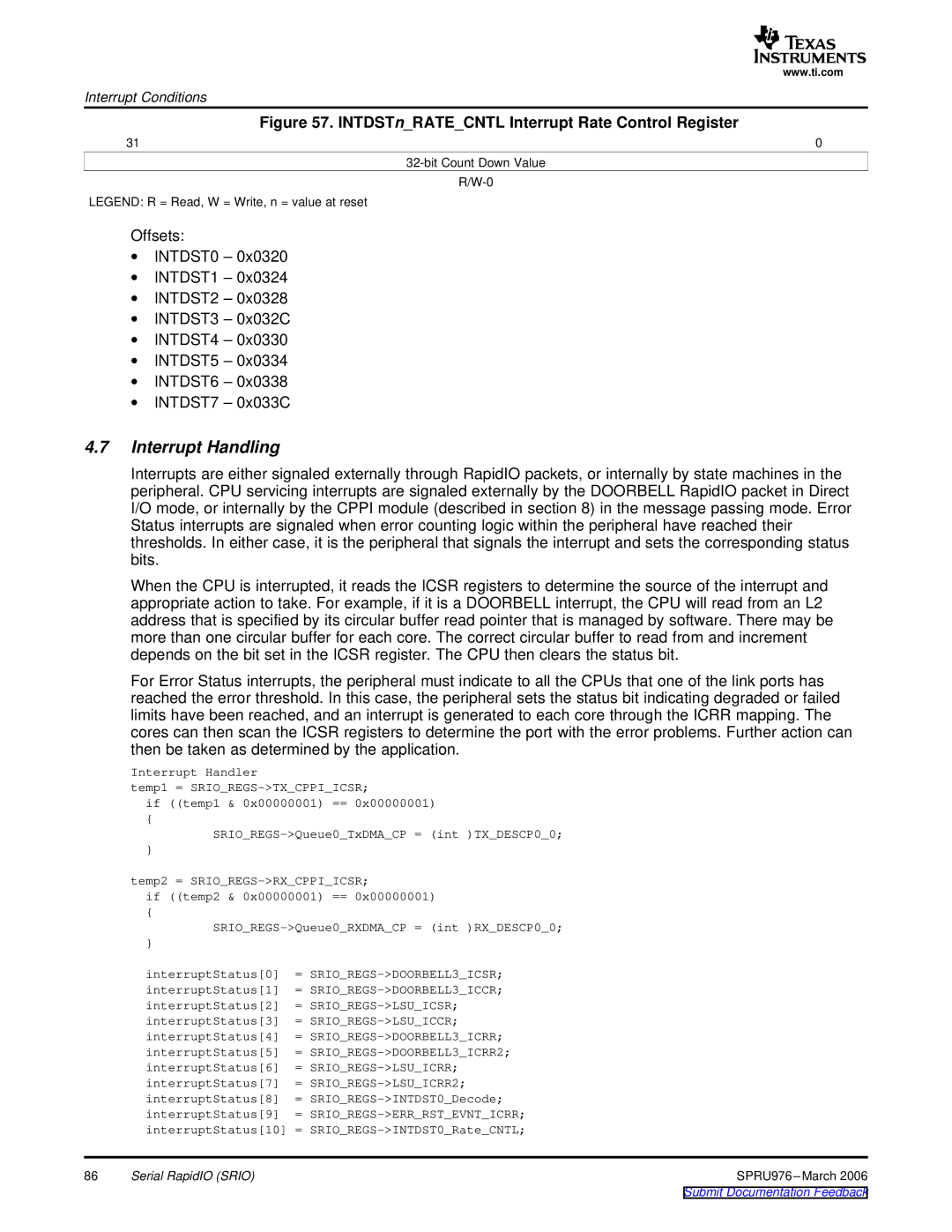

Figure 57. INTDSTn_RATE_CNTL Interrupt Rate Control Register

31 | 0 |

LEGEND: R = Read, W = Write, n = value at reset

Offsets:

∙INTDST0 – 0x0320

∙INTDST1 – 0x0324

∙INTDST2 – 0x0328

∙INTDST3 – 0x032C

∙INTDST4 – 0x0330

∙INTDST5 – 0x0334

∙INTDST6 – 0x0338

∙INTDST7 – 0x033C

4.7Interrupt Handling

Interrupts are either signaled externally through RapidIO packets, or internally by state machines in the peripheral. CPU servicing interrupts are signaled externally by the DOORBELL RapidIO packet in Direct I/O mode, or internally by the CPPI module (described in section 8) in the message passing mode. Error Status interrupts are signaled when error counting logic within the peripheral have reached their thresholds. In either case, it is the peripheral that signals the interrupt and sets the corresponding status bits.

When the CPU is interrupted, it reads the ICSR registers to determine the source of the interrupt and appropriate action to take. For example, if it is a DOORBELL interrupt, the CPU will read from an L2 address that is specified by its circular buffer read pointer that is managed by software. There may be more than one circular buffer for each core. The correct circular buffer to read from and increment depends on the bit set in the ICSR register. The CPU then clears the status bit.

For Error Status interrupts, the peripheral must indicate to all the CPUs that one of the link ports has reached the error threshold. In this case, the peripheral sets the status bit indicating degraded or failed limits have been reached, and an interrupt is generated to each core through the ICRR mapping. The cores can then scan the ICSR registers to determine the port with the error problems. Further action can then be taken as determined by the application.

Interrupt Handler

temp1 =

if ((temp1 & 0x00000001) == 0x00000001)

{

}

temp2 =

if ((temp2 & 0x00000001) == 0x00000001)

{

}

interruptStatus[0] =

86 | Serial RapidIO (SRIO) | SPRU976 |