www.ti.com

SRIO Functional Description

2.3.2SERDES and its Configurations

SRIO offers many benefits to customers by allowing a scalable

Additionally, there are some valuable features built into TI SERDES. System optimization can be uniquely managed to meet individual customer applications. For example, control registers within the SERDES allow you to adjust the TX differential output voltage (Vod) on a per driver basis. This allows power savings on short trace links (on the same board) by reducing the TX swing. Similarly, data edge rates can be adjusted through the control registers to help reduce any EMI affects. Unused links can be individually powered down without affecting the working links.

Because the

The SERDES is a

2.3.2.1Enabling the PLL

The Physical layer SERDES has a

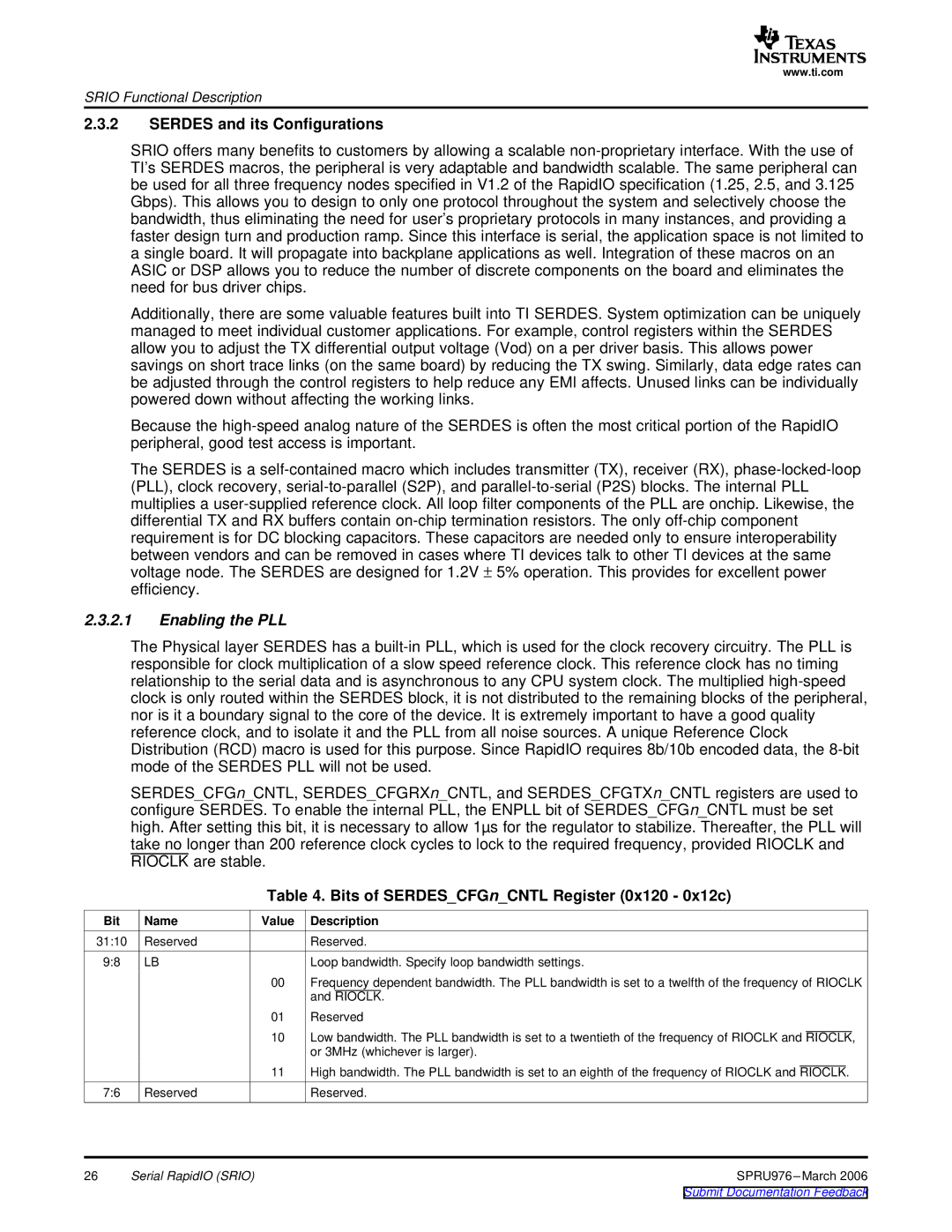

SERDES_CFGn_CNTL, SERDES_CFGRXn_CNTL, and SERDES_CFGTXn_CNTL registers are used to configure SERDES. To enable the internal PLL, the ENPLL bit of SERDES_CFGn_CNTL must be set high. After setting this bit, it is necessary to allow 1µs for the regulator to stabilize. Thereafter, the PLL will take no longer than 200 reference clock cycles to lock to the required frequency, provided RIOCLK and RIOCLK are stable.

|

| Table 4. Bits of SERDES_CFGn_CNTL Register (0x120 - 0x12c) |

Bit | Name | Value Description |

31:10 | Reserved | Reserved. |

9:8 | LB | Loop bandwidth. Specify loop bandwidth settings. |

00Frequency dependent bandwidth. The PLL bandwidth is set to a twelfth of the frequency of RIOCLK and RIOCLK.

01 | Reserved |

10Low bandwidth. The PLL bandwidth is set to a twentieth of the frequency of RIOCLK and RIOCLK, or 3MHz (whichever is larger).

| 11 | High bandwidth. The PLL bandwidth is set to an eighth of the frequency of RIOCLK and RIOCLK. |

7:6 | Reserved | Reserved. |

26 | Serial RapidIO (SRIO) | SPRU976 |