www.ti.com

SRIO Functional Description

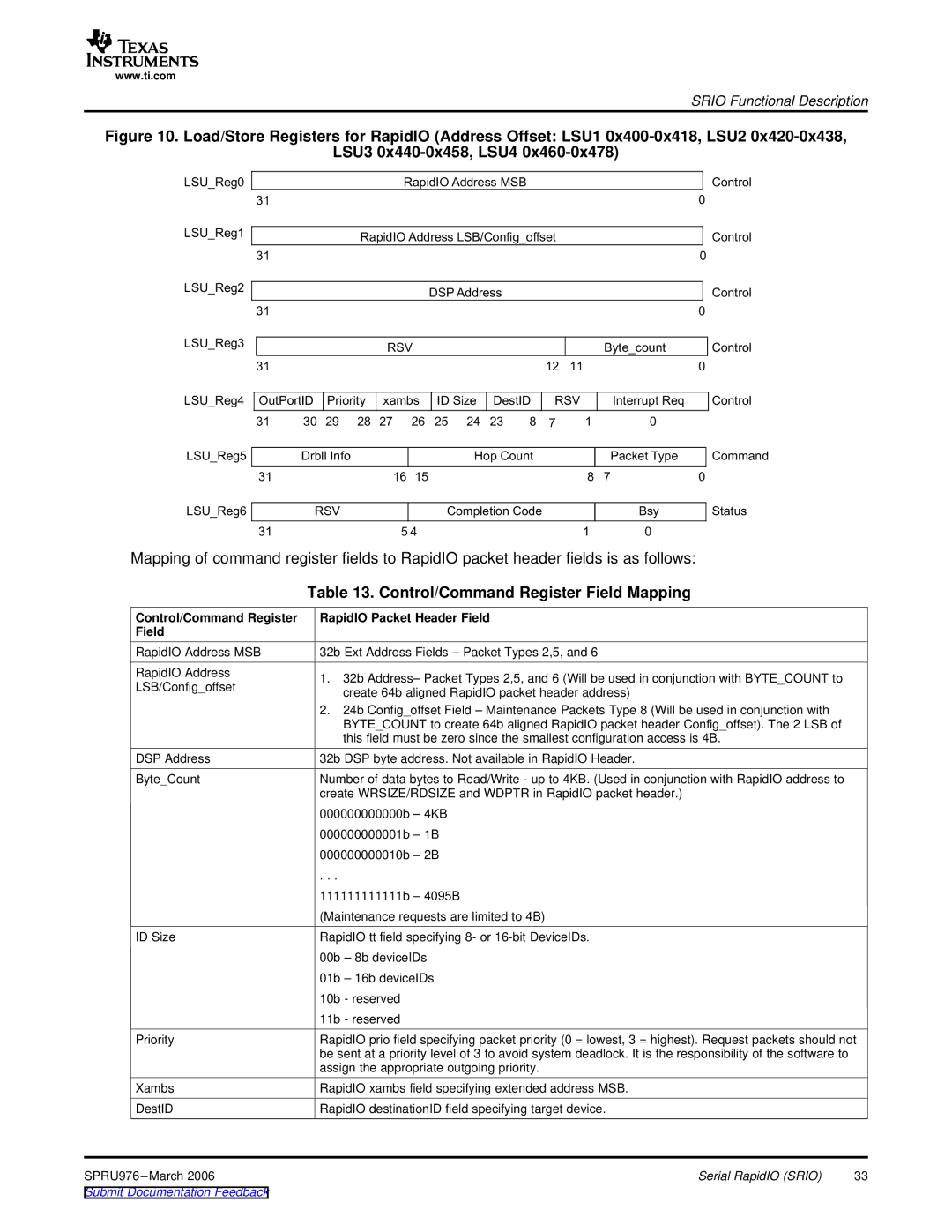

Figure 10. Load/Store Registers for RapidIO (Address Offset: LSU1 0x400-0x418, LSU2 0x420-0x438,

LSU3 0x440-0x458, LSU4 0x460-0x478)

LSU_Reg0

RapidIO Address |

| Control |

31 | 0 | |

LSU_Reg1

RapidIO Address | fset |

| Control |

31 |

| 0 | |

LSU_Reg2

DSP Address |

| Control |

31 | 0 | |

LSU_Reg3

RSV |

| Byte_count |

| Control |

31 | 12 | 11 | 0 |

|

LSU_Reg4

OutPortID | Priority | xambs | ID |

| DestID | RSV |

| Interrupt | ||||

|

|

|

|

|

|

|

|

|

|

|

|

|

31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 8 | 7 | 1 | 0 |

Control

LSU_Reg5

| Drbll |

| Hop | Packet Type |

|

|

|

|

|

|

|

31 | 16 | 15 | 8 | 7 | 0 |

Command

LSU_Reg6

RSV |

| Completion |

| Bsy |

|

|

|

|

|

31 | 5 4 | 1 | 0 | |

Status

Mapping of command register fields to RapidIO packet header fields is as follows:

| Table 13. Control/Command Register Field Mapping |

|

Control/Command Register | RapidIO Packet Header Field |

|

Field |

|

|

RapidIO Address MSB | 32b Ext Address Fields – Packet Types 2,5, and 6 |

|

RapidIO Address | 1. 32b Address– Packet Types 2,5, and 6 (Will be used in conjunction with BYTE_COUNT to |

|

LSB/Config_offset |

| |

create 64b aligned RapidIO packet header address) |

| |

|

| |

| 2. 24b Config_offset Field – Maintenance Packets Type 8 (Will be used in conjunction with |

|

| BYTE_COUNT to create 64b aligned RapidIO packet header Config_offset). The 2 LSB of |

|

| this field must be zero since the smallest configuration access is 4B. |

|

DSP Address | 32b DSP byte address. Not available in RapidIO Header. |

|

Byte_Count | Number of data bytes to Read/Write - up to 4KB. (Used in conjunction with RapidIO address to |

|

| create WRSIZE/RDSIZE and WDPTR in RapidIO packet header.) |

|

| 000000000000b – 4KB |

|

| 000000000001b – 1B |

|

| 000000000010b – 2B |

|

| . . . |

|

| 111111111111b – 4095B |

|

| (Maintenance requests are limited to 4B) |

|

ID Size | RapidIO tt field specifying 8- or |

|

| 00b – 8b deviceIDs |

|

| 01b – 16b deviceIDs |

|

| 10b - reserved |

|

| 11b - reserved |

|

Priority | RapidIO prio field specifying packet priority (0 = lowest, 3 = highest). Request packets should not | |

| be sent at a priority level of 3 to avoid system deadlock. It is the responsibility of the software to |

|

| assign the appropriate outgoing priority. |

|

Xambs | RapidIO xambs field specifying extended address MSB. |

|

DestID | RapidIO destinationID field specifying target device. |

|

SPRU976 | Serial RapidIO (SRIO) | 33 |

Submit Documentation Feedback |

|

|