www.ti.com

Interrupt Conditions

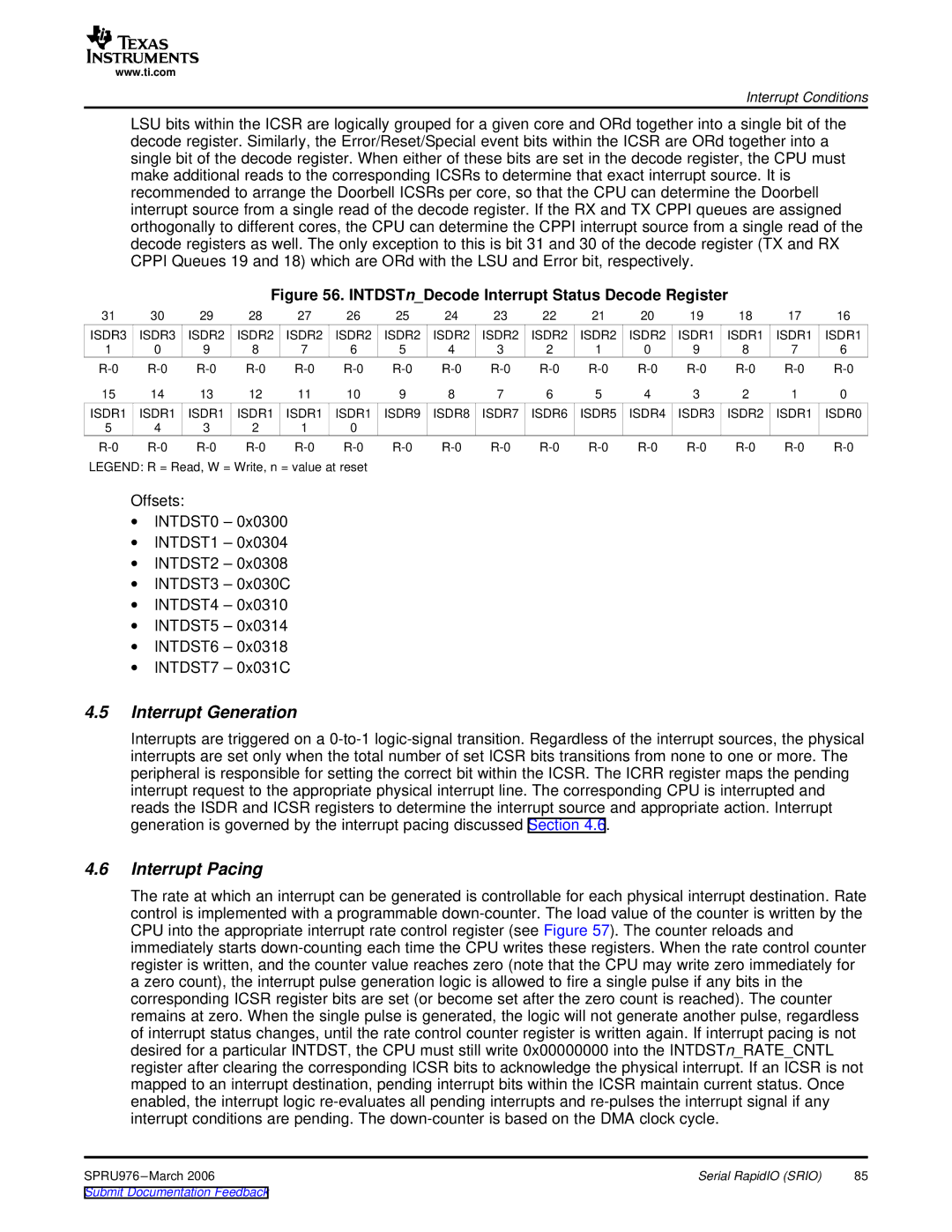

LSU bits within the ICSR are logically grouped for a given core and ORd together into a single bit of the decode register. Similarly, the Error/Reset/Special event bits within the ICSR are ORd together into a single bit of the decode register. When either of these bits are set in the decode register, the CPU must make additional reads to the corresponding ICSRs to determine that exact interrupt source. It is recommended to arrange the Doorbell ICSRs per core, so that the CPU can determine the Doorbell interrupt source from a single read of the decode register. If the RX and TX CPPI queues are assigned orthogonally to different cores, the CPU can determine the CPPI interrupt source from a single read of the decode registers as well. The only exception to this is bit 31 and 30 of the decode register (TX and RX CPPI Queues 19 and 18) which are ORd with the LSU and Error bit, respectively.

Figure 56. INTDSTn_Decode Interrupt Status Decode Register

31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

ISDR3 | ISDR3 | ISDR2 | ISDR2 | ISDR2 | ISDR2 | ISDR2 | ISDR2 | ISDR2 | ISDR2 | ISDR2 | ISDR2 | ISDR1 | ISDR1 | ISDR1 | ISDR1 |

1 | 0 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | 9 | 8 | 7 | 6 |

15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

ISDR1 | ISDR1 | ISDR1 | ISDR1 | ISDR1 | ISDR1 | ISDR9 | ISDR8 | ISDR7 | ISDR6 | ISDR5 | ISDR4 | ISDR3 | ISDR2 | ISDR1 | ISDR0 |

5 | 4 | 3 | 2 | 1 | 0 |

|

|

|

|

|

|

|

|

|

|

LEGEND: R = Read, W = Write, n = value at reset

Offsets:

∙INTDST0 – 0x0300

∙INTDST1 – 0x0304

∙INTDST2 – 0x0308

∙INTDST3 – 0x030C

∙INTDST4 – 0x0310

∙INTDST5 – 0x0314

∙INTDST6 – 0x0318

∙INTDST7 – 0x031C

4.5Interrupt Generation

Interrupts are triggered on a

4.6Interrupt Pacing

The rate at which an interrupt can be generated is controllable for each physical interrupt destination. Rate control is implemented with a programmable

SPRU976 | Serial RapidIO (SRIO) | 85 |