www.ti.com

SRIO Registers

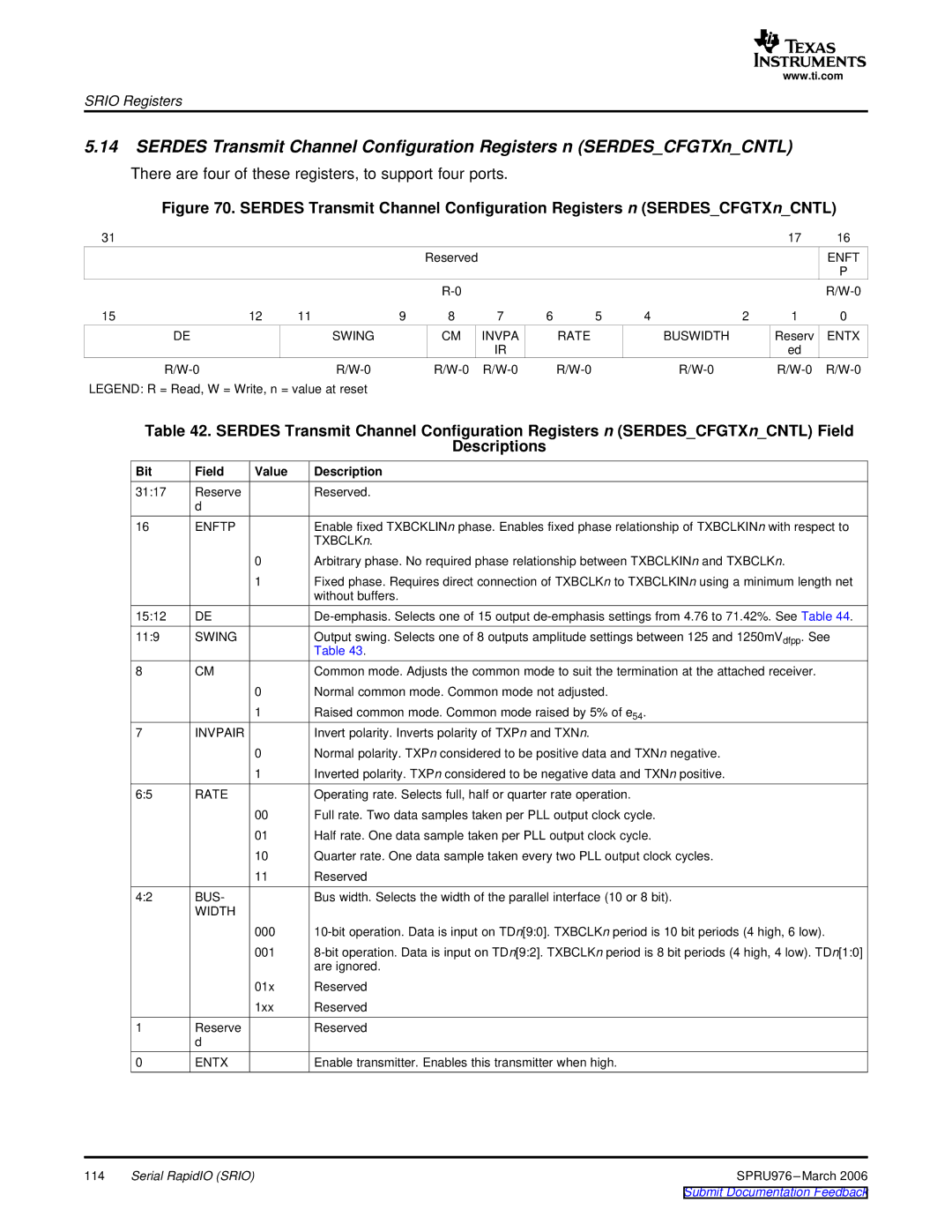

5.14SERDES Transmit Channel Configuration Registers n (SERDES_CFGTXn_CNTL)

There are four of these registers, to support four ports.

Figure 70. SERDES Transmit Channel Configuration Registers n (SERDES_CFGTXn_CNTL)

31 |

|

|

|

|

|

|

|

|

| 17 | 16 |

|

|

|

| Reserved |

|

|

|

|

|

| ENFT |

|

|

|

|

|

|

|

|

|

|

| P |

|

|

|

|

|

|

|

|

|

| ||

15 | 12 | 11 | 9 | 8 | 7 | 6 | 5 | 4 | 2 | 1 | 0 |

DE |

| SWING |

| CM | INVPA |

| RATE |

| BUSWIDTH | Reserv | ENTX |

|

|

|

|

| IR |

|

|

|

| ed |

|

|

|

|

|

LEGEND: R = Read, W = Write, n = value at reset

Table 42. SERDES Transmit Channel Configuration Registers n (SERDES_CFGTXn_CNTL) Field

Descriptions

Bit | Field | Value | Description |

31:17 | Reserve |

| Reserved. |

| d |

|

|

16 | ENFTP |

| Enable fixed TXBCKLINn phase. Enables fixed phase relationship of TXBCLKINn with respect to |

|

|

| TXBCLKn. |

|

| 0 | Arbitrary phase. No required phase relationship between TXBCLKINn and TXBCLKn. |

1Fixed phase. Requires direct connection of TXBCLKn to TXBCLKINn using a minimum length net without buffers.

15:12 | DE | |

11:9 | SWING | Output swing. Selects one of 8 outputs amplitude settings between 125 and 1250mVdfpp. See |

|

| Table 43. |

8 | CM | Common mode. Adjusts the common mode to suit the termination at the attached receiver. |

| 0 | Normal common mode. Common mode not adjusted. |

| 1 | Raised common mode. Common mode raised by 5% of e54. |

7 | INVPAIR | Invert polarity. Inverts polarity of TXPn and TXNn. |

| 0 | Normal polarity. TXPn considered to be positive data and TXNn negative. |

| 1 | Inverted polarity. TXPn considered to be negative data and TXNn positive. |

6:5 | RATE | Operating rate. Selects full, half or quarter rate operation. |

| 00 | Full rate. Two data samples taken per PLL output clock cycle. |

| 01 | Half rate. One data sample taken per PLL output clock cycle. |

| 10 | Quarter rate. One data sample taken every two PLL output clock cycles. |

| 11 | Reserved |

4:2 | BUS- | Bus width. Selects the width of the parallel interface (10 or 8 bit). |

| WIDTH |

|

| 000 |

001

| 01x | Reserved |

| 1xx | Reserved |

1 | Reserve | Reserved |

| d |

|

0 | ENTX | Enable transmitter. Enables this transmitter when high. |

114 | Serial RapidIO (SRIO) | SPRU976 |

|

| Submit Documentation Feedback |