www.ti.com

SRIO Functional Description

2.3.8Endianness

RapidIO is based on big endian. This is discussed in detail in section 2.4 of the RapidIO Interconnect specification. Essentially, big endian specifies the address ordering as the most significant bit/byte first. For example, in the

All endian specific conversion is handled within the peripheral. For

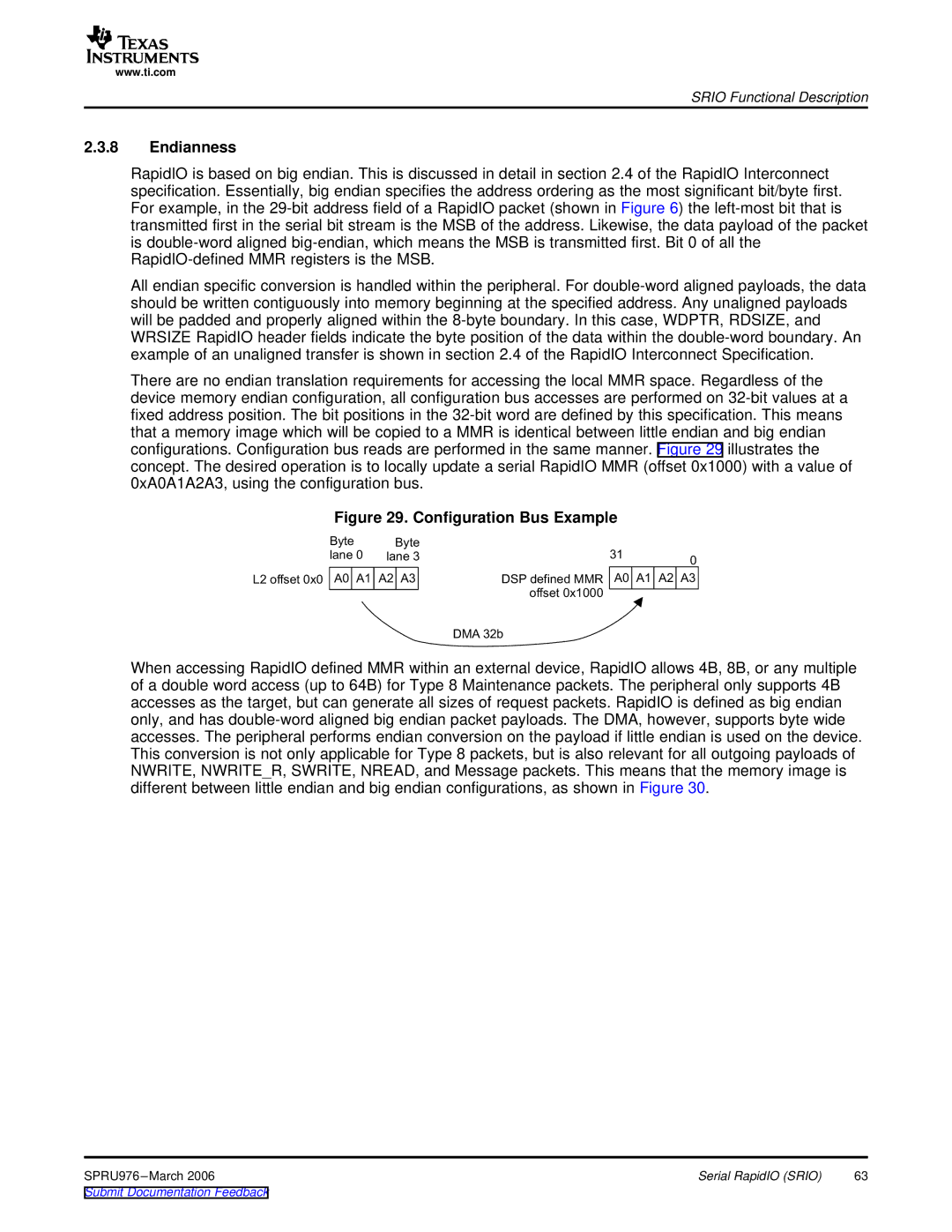

There are no endian translation requirements for accessing the local MMR space. Regardless of the device memory endian configuration, all configuration bus accesses are performed on

Figure 29. Configuration Bus Example

L2 fset

Byte | Byte |

| |||

lane | lane |

| |||

|

|

|

|

|

|

A0 | A1 | A2 | A3 |

| DSP defined |

|

|

|

|

| offset |

|

|

|

|

| |

|

|

|

|

| DMA 32b |

310

A0 A1 A2 A3

When accessing RapidIO defined MMR within an external device, RapidIO allows 4B, 8B, or any multiple of a double word access (up to 64B) for Type 8 Maintenance packets. The peripheral only supports 4B accesses as the target, but can generate all sizes of request packets. RapidIO is defined as big endian only, and has

SPRU976 | Serial RapidIO (SRIO) | 63 |