www.ti.com

SRIO Registers

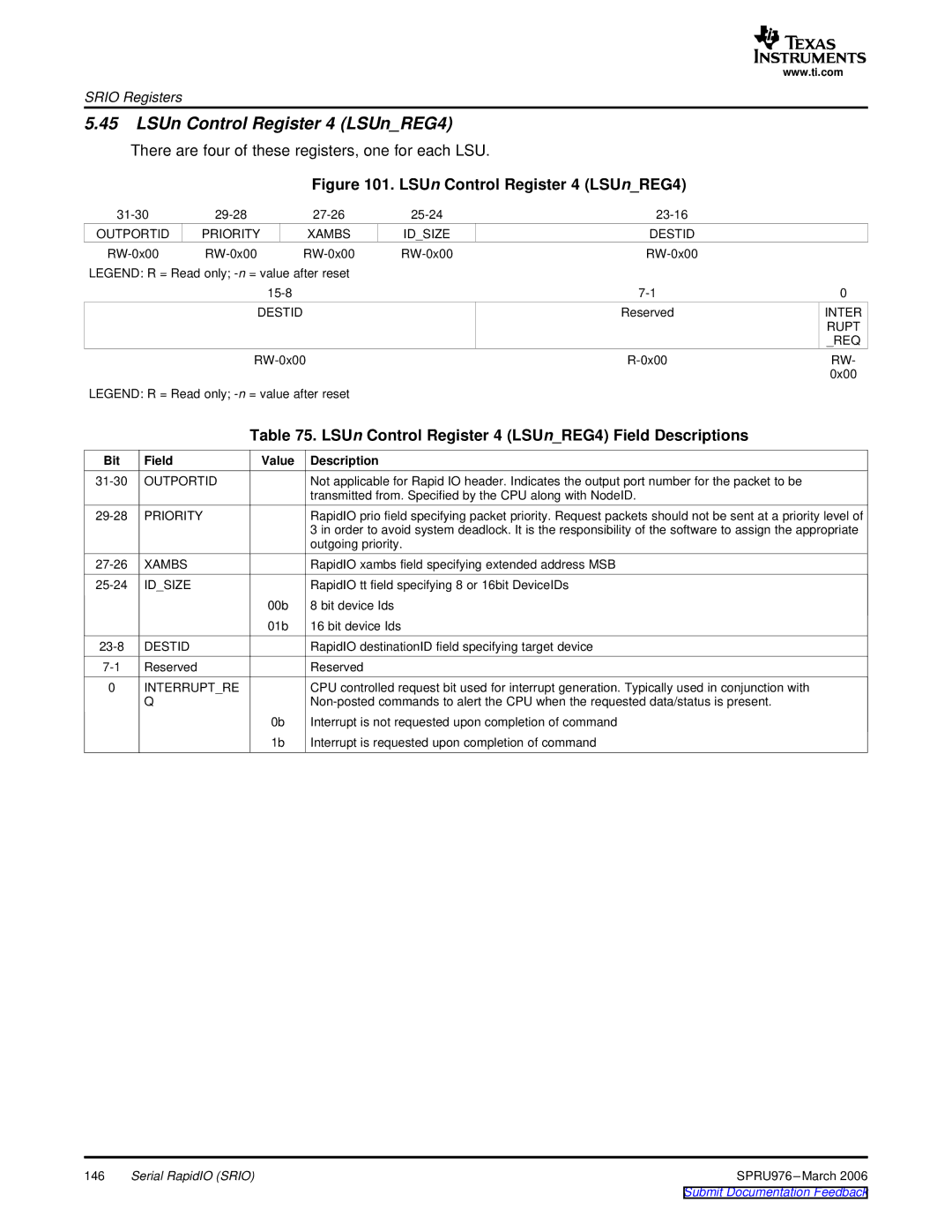

5.45LSUn Control Register 4 (LSUn_REG4)

There are four of these registers, one for each LSU.

Figure 101. LSUn Control Register 4 (LSUn_REG4)

| |||||

OUTPORTID | PRIORITY | XAMBS | ID_SIZE | DESTID |

|

| |||||

LEGEND: R = Read only; |

|

|

| ||

|

|

| 0 | ||

| DESTID |

|

| Reserved | INTER |

|

|

|

|

| RUPT |

|

|

|

|

| _REQ |

|

| RW- | |||

|

|

|

|

| 0x00 |

LEGEND: R = Read only;

Table 75. LSUn Control Register 4 (LSUn_REG4) Field Descriptions

Bit | Field | Value | Description |

OUTPORTID |

| Not applicable for Rapid IO header. Indicates the output port number for the packet to be | |

|

|

| transmitted from. Specified by the CPU along with NodeID. |

PRIORITY |

| RapidIO prio field specifying packet priority. Request packets should not be sent at a priority level of | |

|

|

| 3 in order to avoid system deadlock. It is the responsibility of the software to assign the appropriate |

|

|

| outgoing priority. |

XAMBS |

| RapidIO xambs field specifying extended address MSB | |

ID_SIZE |

| RapidIO tt field specifying 8 or 16bit DeviceIDs | |

|

| 00b | 8 bit device Ids |

|

| 01b | 16 bit device Ids |

DESTID |

| RapidIO destinationID field specifying target device | |

Reserved |

| Reserved | |

0 | INTERRUPT_RE |

| CPU controlled request bit used for interrupt generation. Typically used in conjunction with |

| Q |

| |

|

| 0b | Interrupt is not requested upon completion of command |

|

| 1b | Interrupt is requested upon completion of command |

146 | Serial RapidIO (SRIO) | SPRU976 |