www.ti.com

SRIO Functional Description

This allows the letter and mailbox fields to instead allow four concurrent

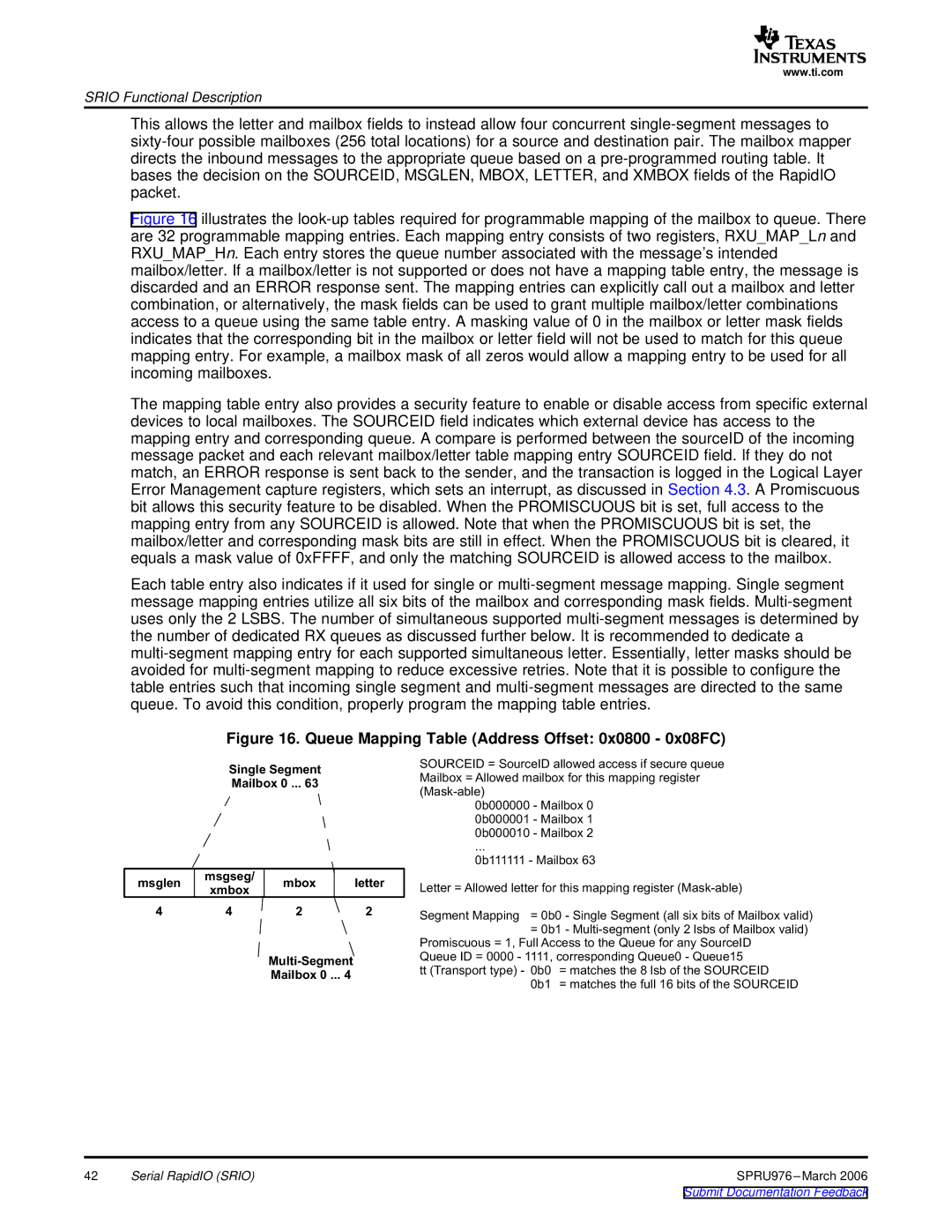

Figure 16 illustrates the look-up tables required for programmable mapping of the mailbox to queue. There are 32 programmable mapping entries. Each mapping entry consists of two registers, RXU_MAP_Ln and RXU_MAP_Hn. Each entry stores the queue number associated with the message’s intended mailbox/letter. If a mailbox/letter is not supported or does not have a mapping table entry, the message is discarded and an ERROR response sent. The mapping entries can explicitly call out a mailbox and letter combination, or alternatively, the mask fields can be used to grant multiple mailbox/letter combinations access to a queue using the same table entry. A masking value of 0 in the mailbox or letter mask fields indicates that the corresponding bit in the mailbox or letter field will not be used to match for this queue mapping entry. For example, a mailbox mask of all zeros would allow a mapping entry to be used for all incoming mailboxes.

The mapping table entry also provides a security feature to enable or disable access from specific external devices to local mailboxes. The SOURCEID field indicates which external device has access to the mapping entry and corresponding queue. A compare is performed between the sourceID of the incoming message packet and each relevant mailbox/letter table mapping entry SOURCEID field. If they do not match, an ERROR response is sent back to the sender, and the transaction is logged in the Logical Layer Error Management capture registers, which sets an interrupt, as discussed in Section 4.3. A Promiscuous bit allows this security feature to be disabled. When the PROMISCUOUS bit is set, full access to the mapping entry from any SOURCEID is allowed. Note that when the PROMISCUOUS bit is set, the mailbox/letter and corresponding mask bits are still in effect. When the PROMISCUOUS bit is cleared, it equals a mask value of 0xFFFF, and only the matching SOURCEID is allowed access to the mailbox.

Each table entry also indicates if it used for single or multi-segment message mapping. Single segment message mapping entries utilize all six bits of the mailbox and corresponding mask fields. Multi-segment uses only the 2 LSBS. The number of simultaneous supported multi-segment messages is determined by the number of dedicated RX queues as discussed further below. It is recommended to dedicate a multi-segment mapping entry for each supported simultaneous letter. Essentially, letter masks should be avoided for multi-segment mapping to reduce excessive retries. Note that it is possible to configure the table entries such that incoming single segment and multi-segment messages are directed to the same queue. To avoid this condition, properly program the mapping table entries.

Figure 16. Queue Mapping Table (Address Offset: 0x0800 - 0x08FC)

Single

Mailbox

msglen | msgseg/ | mbox |

| letter |

xmbox |

| |||

|

|

|

| |

4 | 4 | 2 |

| 2 |

|

|

| ||

|

| Mailbox |

| |

SOURCEID Mailbox Allowed

0b000000

0b000001

0b000010

...

0b111111

Letter Allowed |

|

|

Segment | = |

|

| = |

|

Promiscuous | Access | |

Queue | 111, |

|

tt ransport | 0b0 | = |

| 0b1 | = |

42 | Serial RapidIO (SRIO) | SPRU976 |