www.ti.com

SRIO Registers

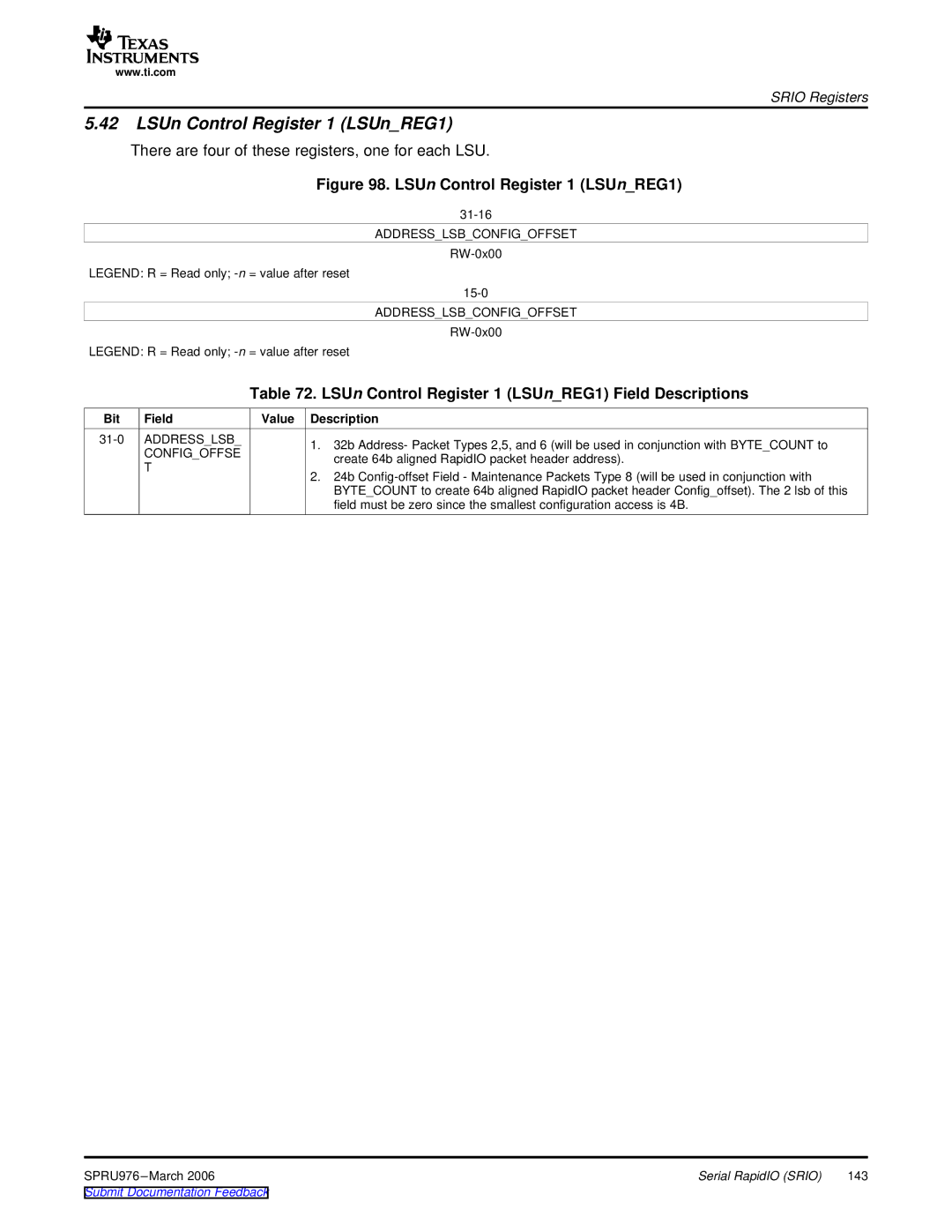

5.42LSUn Control Register 1 (LSUn_REG1)

There are four of these registers, one for each LSU.

Figure 98. LSUn Control Register 1 (LSUn_REG1)

ADDRESS_LSB_CONFIG_OFFSET

LEGEND: R = Read only;

ADDRESS_LSB_CONFIG_OFFSET

LEGEND: R = Read only;

| Table 72. LSUn Control Register 1 (LSUn_REG1) Field Descriptions |

Bit Field | Value Description |

31-0 ADDRESS_LSB_

CONFIG_OFFSE T

1.32b Address- Packet Types 2,5, and 6 (will be used in conjunction with BYTE_COUNT to create 64b aligned RapidIO packet header address).

2.24b

SPRU976 | Serial RapidIO (SRIO) | 143 |