www.ti.com

SRIO Registers

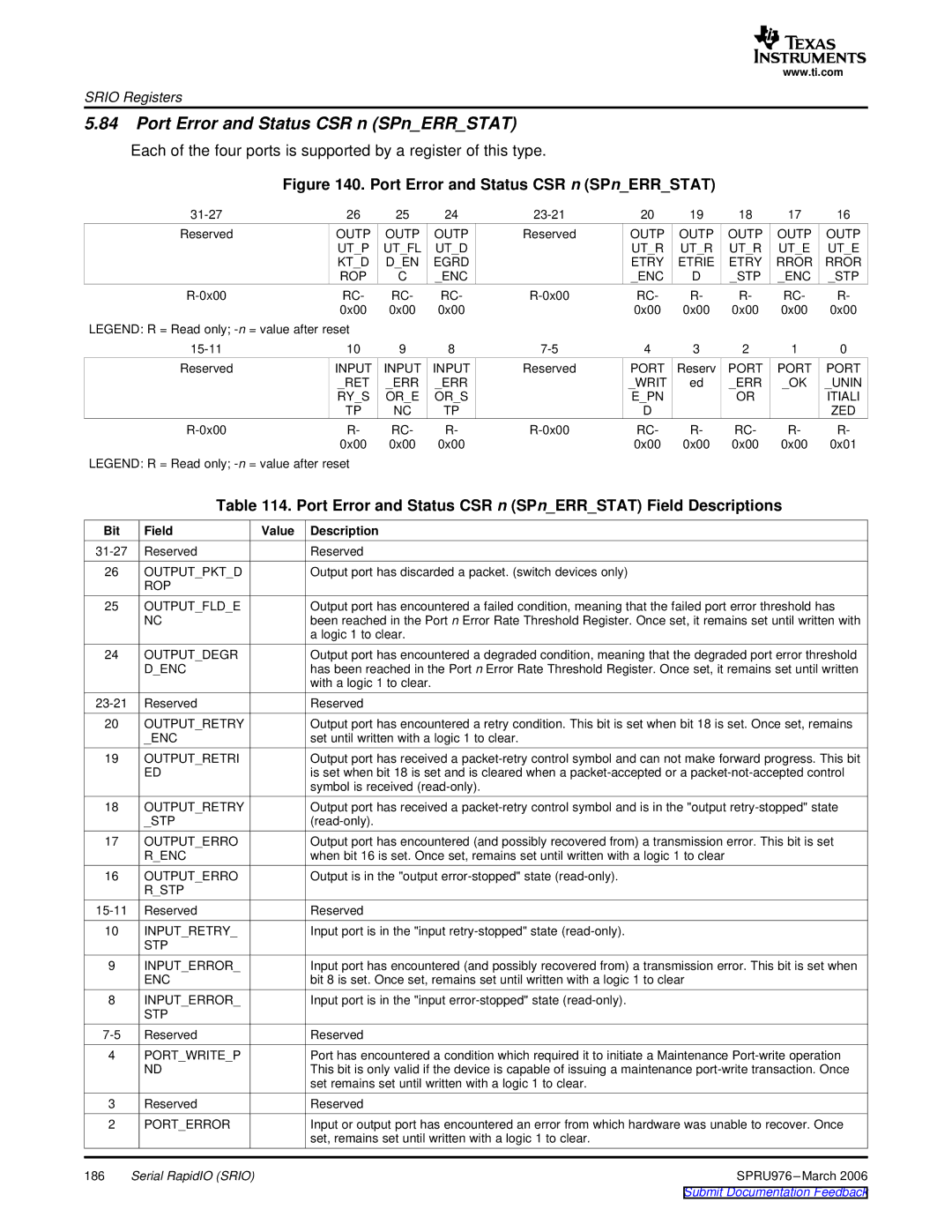

5.84Port Error and Status CSR n (SPn_ERR_STAT)

Each of the four ports is supported by a register of this type.

Figure 140. Port Error and Status CSR n (SPn_ERR_STAT)

26 | 25 | 24 | 20 | 19 | 18 | 17 | 16 | ||

Reserved | OUTP | OUTP | OUTP | Reserved | OUTP | OUTP | OUTP | OUTP | OUTP |

| UT_P UT_FL UT_D |

| UT_R UT_R | UT_R UT_E UT_E | |||||

| KT_D D_EN EGRD |

| ETRY | ETRIE | ETRY | RROR | RROR | ||

| ROP | C | _ENC |

| _ENC | D | _STP | _ENC | _STP |

RC- | RC- | RC- | RC- | R- | R- | RC- | R- | ||

| 0x00 | 0x00 | 0x00 |

| 0x00 | 0x00 | 0x00 | 0x00 | 0x00 |

LEGEND: R = Read only; |

|

|

|

|

|

|

|

| |

10 | 9 | 8 | 4 | 3 | 2 | 1 | 0 | ||

Reserved | INPUT | INPUT | INPUT | Reserved | PORT | Reserv | PORT | PORT | PORT |

| _RET _ERR _ERR |

| _WRIT | ed | _ERR | _OK | _UNIN | ||

| RY_S OR_E OR_S |

| E_PN |

| OR |

| ITIALI | ||

| TP | NC | TP |

| D |

|

|

| ZED |

R- | RC- | R- | RC- | R- | RC- | R- | R- | ||

| 0x00 | 0x00 | 0x00 |

| 0x00 | 0x00 | 0x00 | 0x00 | 0x01 |

LEGEND: R = Read only;

Table 114. Port Error and Status CSR n (SPn_ERR_STAT) Field Descriptions

Bit | Field | Value | Description |

Reserved |

| Reserved | |

26 | OUTPUT_PKT_D |

| Output port has discarded a packet. (switch devices only) |

| ROP |

|

|

25 | OUTPUT_FLD_E |

| Output port has encountered a failed condition, meaning that the failed port error threshold has |

| NC |

| been reached in the Port n Error Rate Threshold Register. Once set, it remains set until written with |

|

|

| a logic 1 to clear. |

24 | OUTPUT_DEGR |

| Output port has encountered a degraded condition, meaning that the degraded port error threshold |

| D_ENC |

| has been reached in the Port n Error Rate Threshold Register. Once set, it remains set until written |

|

|

| with a logic 1 to clear. |

Reserved |

| Reserved | |

20 | OUTPUT_RETRY |

| Output port has encountered a retry condition. This bit is set when bit 18 is set. Once set, remains |

| _ENC |

| set until written with a logic 1 to clear. |

19 | OUTPUT_RETRI |

| Output port has received a |

| ED |

| is set when bit 18 is set and is cleared when a |

|

|

| symbol is received |

18 | OUTPUT_RETRY |

| Output port has received a |

| _STP |

| |

17 | OUTPUT_ERRO |

| Output port has encountered (and possibly recovered from) a transmission error. This bit is set |

| R_ENC |

| when bit 16 is set. Once set, remains set until written with a logic 1 to clear |

16 | OUTPUT_ERRO |

| Output is in the "output |

| R_STP |

|

|

Reserved |

| Reserved | |

10 | INPUT_RETRY_ |

| Input port is in the "input |

| STP |

|

|

9 | INPUT_ERROR_ |

| Input port has encountered (and possibly recovered from) a transmission error. This bit is set when |

| ENC |

| bit 8 is set. Once set, remains set until written with a logic 1 to clear |

8 | INPUT_ERROR_ |

| Input port is in the "input |

| STP |

|

|

Reserved |

| Reserved | |

4 | PORT_WRITE_P |

| Port has encountered a condition which required it to initiate a Maintenance |

| ND |

| This bit is only valid if the device is capable of issuing a maintenance |

|

|

| set remains set until written with a logic 1 to clear. |

3 | Reserved |

| Reserved |

2 | PORT_ERROR |

| Input or output port has encountered an error from which hardware was unable to recover. Once |

|

|

| set, remains set until written with a logic 1 to clear. |

186 | Serial RapidIO (SRIO) |

| SPRU976 |