www.ti.com

SRIO Functional Description

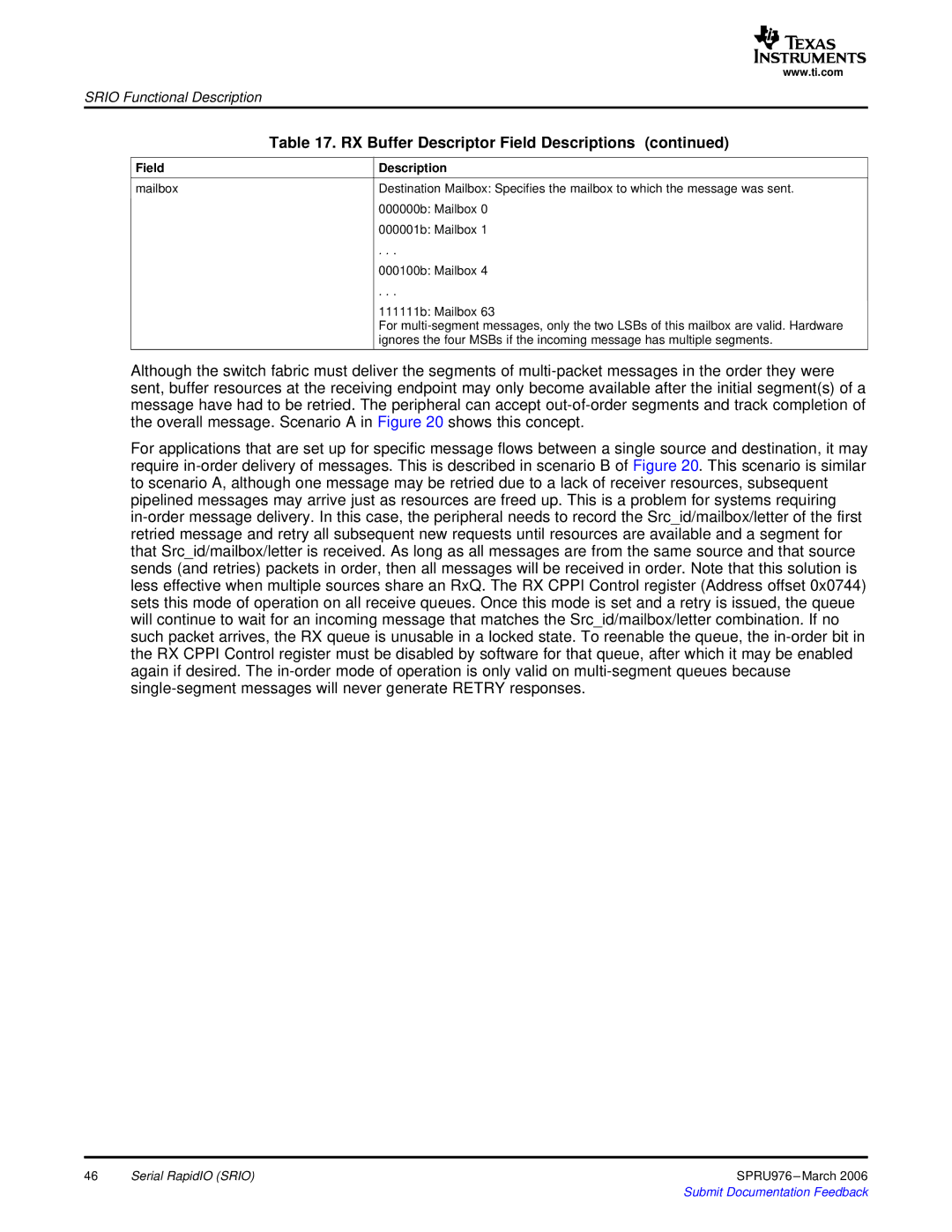

| Table 17. RX Buffer Descriptor Field Descriptions (continued) |

Field | Description |

mailbox | Destination Mailbox: Specifies the mailbox to which the message was sent. |

| 000000b: Mailbox 0 |

| 000001b: Mailbox 1 |

| . . . |

| 000100b: Mailbox 4 |

| . . . |

| 111111b: Mailbox 63 |

| For |

| ignores the four MSBs if the incoming message has multiple segments. |

Although the switch fabric must deliver the segments of

For applications that are set up for specific message flows between a single source and destination, it may require

46 | Serial RapidIO (SRIO) | SPRU976 |