www.ti.com

SRIO Functional Description

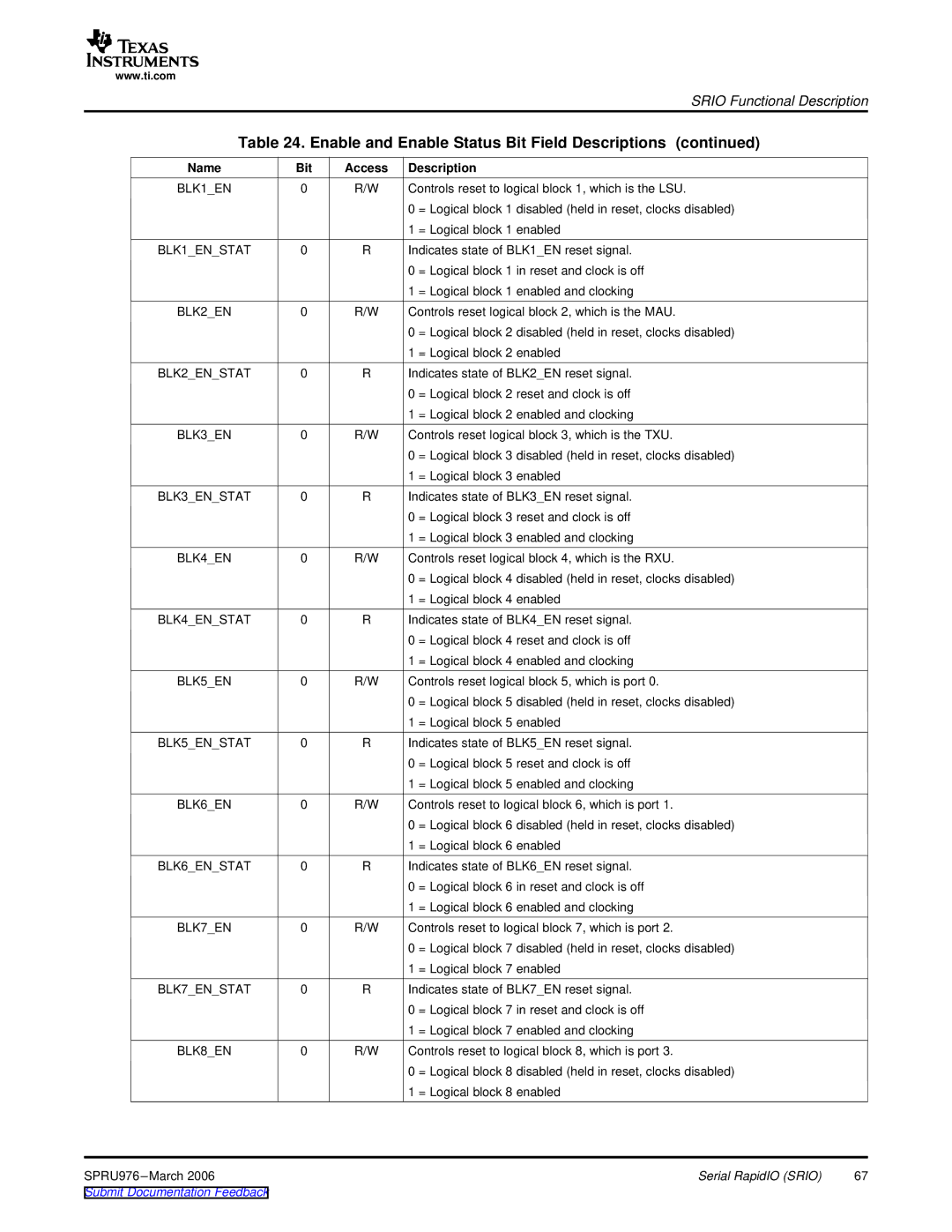

Table 24. Enable and Enable Status Bit Field Descriptions (continued)

Name | Bit | Access | Description | |

BLK1_EN | 0 | R/W | Controls reset to logical block 1, which is the LSU. | |

|

|

| 0 | = Logical block 1 disabled (held in reset, clocks disabled) |

|

|

| 1 | = Logical block 1 enabled |

BLK1_EN_STAT | 0 | R | Indicates state of BLK1_EN reset signal. | |

|

|

| 0 | = Logical block 1 in reset and clock is off |

|

|

| 1 | = Logical block 1 enabled and clocking |

BLK2_EN | 0 | R/W | Controls reset logical block 2, which is the MAU. | |

|

|

| 0 | = Logical block 2 disabled (held in reset, clocks disabled) |

|

|

| 1 | = Logical block 2 enabled |

BLK2_EN_STAT | 0 | R | Indicates state of BLK2_EN reset signal. | |

|

|

| 0 | = Logical block 2 reset and clock is off |

|

|

| 1 | = Logical block 2 enabled and clocking |

BLK3_EN | 0 | R/W | Controls reset logical block 3, which is the TXU. | |

|

|

| 0 | = Logical block 3 disabled (held in reset, clocks disabled) |

|

|

| 1 | = Logical block 3 enabled |

BLK3_EN_STAT | 0 | R | Indicates state of BLK3_EN reset signal. | |

|

|

| 0 | = Logical block 3 reset and clock is off |

|

|

| 1 | = Logical block 3 enabled and clocking |

BLK4_EN | 0 | R/W | Controls reset logical block 4, which is the RXU. | |

|

|

| 0 | = Logical block 4 disabled (held in reset, clocks disabled) |

|

|

| 1 | = Logical block 4 enabled |

BLK4_EN_STAT | 0 | R | Indicates state of BLK4_EN reset signal. | |

|

|

| 0 | = Logical block 4 reset and clock is off |

|

|

| 1 | = Logical block 4 enabled and clocking |

BLK5_EN | 0 | R/W | Controls reset logical block 5, which is port 0. | |

|

|

| 0 | = Logical block 5 disabled (held in reset, clocks disabled) |

|

|

| 1 | = Logical block 5 enabled |

BLK5_EN_STAT | 0 | R | Indicates state of BLK5_EN reset signal. | |

|

|

| 0 | = Logical block 5 reset and clock is off |

|

|

| 1 | = Logical block 5 enabled and clocking |

BLK6_EN | 0 | R/W | Controls reset to logical block 6, which is port 1. | |

|

|

| 0 | = Logical block 6 disabled (held in reset, clocks disabled) |

|

|

| 1 | = Logical block 6 enabled |

BLK6_EN_STAT | 0 | R | Indicates state of BLK6_EN reset signal. | |

|

|

| 0 | = Logical block 6 in reset and clock is off |

|

|

| 1 | = Logical block 6 enabled and clocking |

BLK7_EN | 0 | R/W | Controls reset to logical block 7, which is port 2. | |

|

|

| 0 | = Logical block 7 disabled (held in reset, clocks disabled) |

|

|

| 1 | = Logical block 7 enabled |

BLK7_EN_STAT | 0 | R | Indicates state of BLK7_EN reset signal. | |

|

|

| 0 | = Logical block 7 in reset and clock is off |

|

|

| 1 | = Logical block 7 enabled and clocking |

BLK8_EN | 0 | R/W | Controls reset to logical block 8, which is port 3. | |

|

|

| 0 | = Logical block 8 disabled (held in reset, clocks disabled) |

|

|

| 1 | = Logical block 8 enabled |

SPRU976 | Serial RapidIO (SRIO) | 67 |

Submit Documentation Feedback |

|

|