www.ti.com

SRIO Functional Description

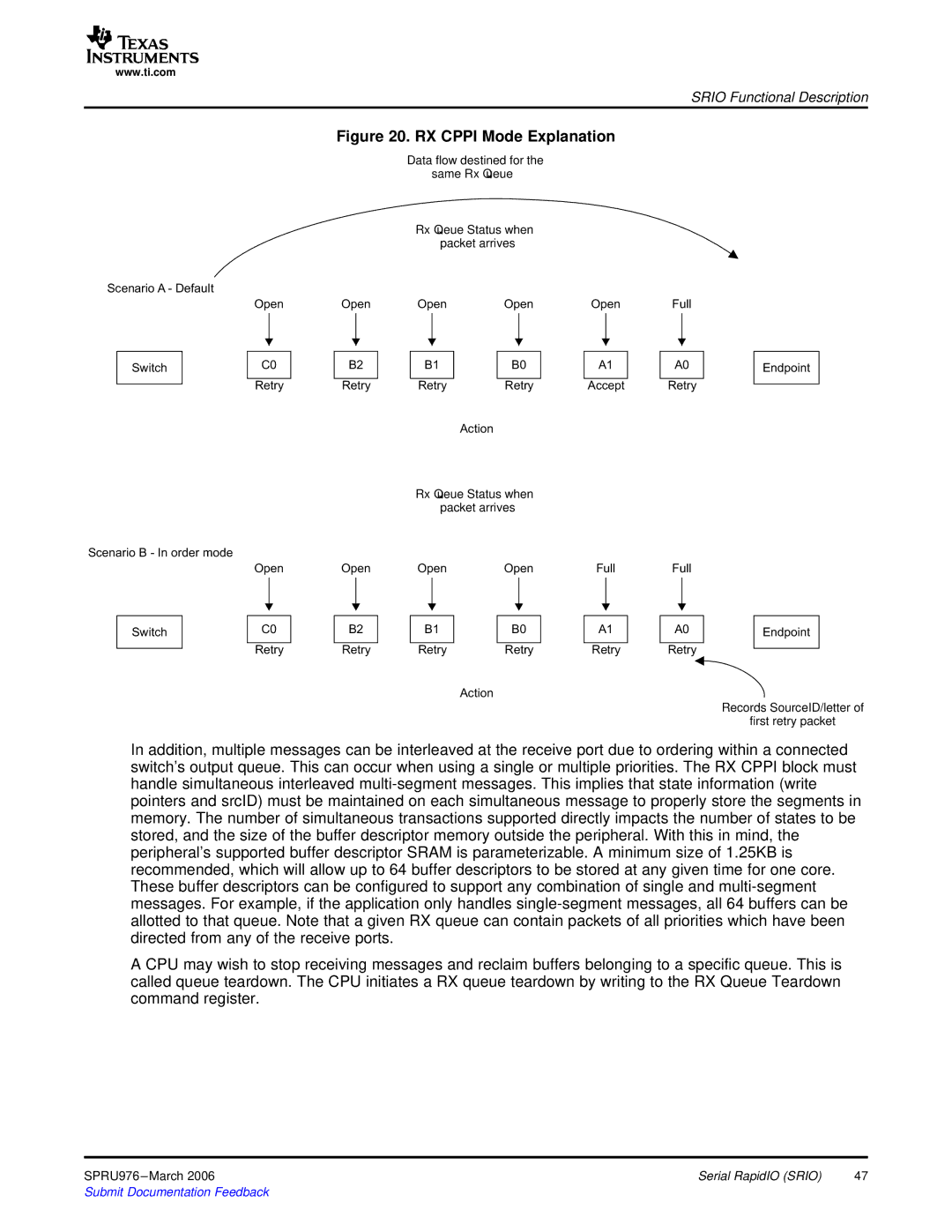

Figure 20. RX CPPI Mode Explanation

Scenario A -

Switch

Scenario

Switch

Open

C0

Retry

Open

C0

Retry

Open

B2

Retry

Open

B2

Retry

Data same

Rx

packet

Open

B1

Retry

Action

Rx

packet

Open

B1

Retry

Action

Open

B0

Retry

Open

B0

Retry

Open

A1

Accept

Full

A1

Retry

Full

A0

Retry

Full

A0

Retry

Endpoint

Endpoint

Records first

In addition, multiple messages can be interleaved at the receive port due to ordering within a connected switch’s output queue. This can occur when using a single or multiple priorities. The RX CPPI block must handle simultaneous interleaved

A CPU may wish to stop receiving messages and reclaim buffers belonging to a specific queue. This is called queue teardown. The CPU initiates a RX queue teardown by writing to the RX Queue Teardown command register.

SPRU976 | Serial RapidIO (SRIO) | 47 |