www.ti.com

SRIO Registers

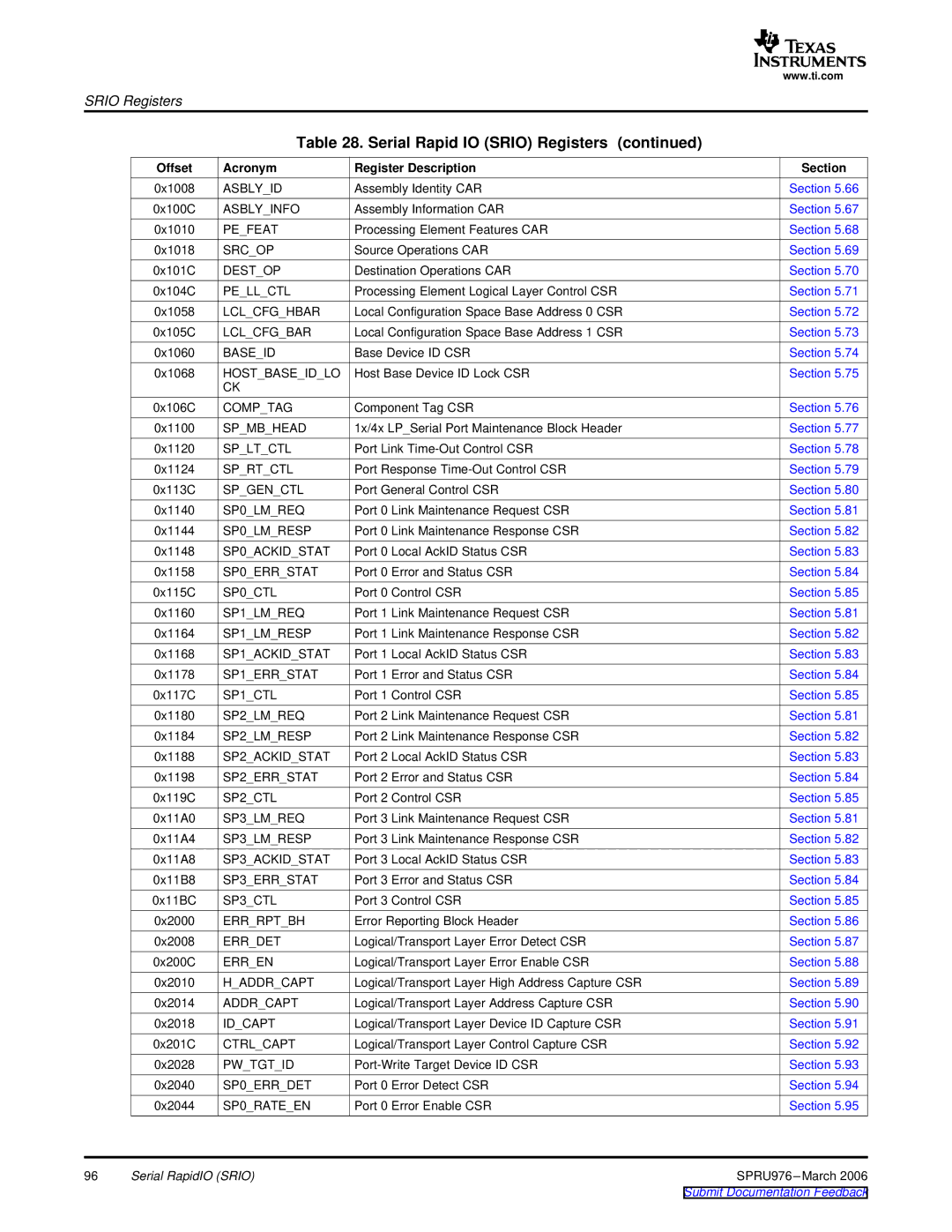

Table 28. Serial Rapid IO (SRIO) Registers (continued)

| Offset | Acronym | Register Description | Section |

| 0x1008 | ASBLY_ID | Assembly Identity CAR | Section 5.66 |

| 0x100C | ASBLY_INFO | Assembly Information CAR | Section 5.67 |

| 0x1010 | PE_FEAT | Processing Element Features CAR | Section 5.68 |

| 0x1018 | SRC_OP | Source Operations CAR | Section 5.69 |

| 0x101C | DEST_OP | Destination Operations CAR | Section 5.70 |

| 0x104C | PE_LL_CTL | Processing Element Logical Layer Control CSR | Section 5.71 |

| 0x1058 | LCL_CFG_HBAR | Local Configuration Space Base Address 0 CSR | Section 5.72 |

| 0x105C | LCL_CFG_BAR | Local Configuration Space Base Address 1 CSR | Section 5.73 |

| 0x1060 | BASE_ID | Base Device ID CSR | Section 5.74 |

| 0x1068 | HOST_BASE_ID_LO | Host Base Device ID Lock CSR | Section 5.75 |

|

| CK |

|

|

| 0x106C | COMP_TAG | Component Tag CSR | Section 5.76 |

| 0x1100 | SP_MB_HEAD | 1x/4x LP_Serial Port Maintenance Block Header | Section 5.77 |

| 0x1120 | SP_LT_CTL | Port Link | Section 5.78 |

| 0x1124 | SP_RT_CTL | Port Response | Section 5.79 |

| 0x113C | SP_GEN_CTL | Port General Control CSR | Section 5.80 |

| 0x1140 | SP0_LM_REQ | Port 0 Link Maintenance Request CSR | Section 5.81 |

| 0x1144 | SP0_LM_RESP | Port 0 Link Maintenance Response CSR | Section 5.82 |

| 0x1148 | SP0_ACKID_STAT | Port 0 Local AckID Status CSR | Section 5.83 |

| 0x1158 | SP0_ERR_STAT | Port 0 Error and Status CSR | Section 5.84 |

| 0x115C | SP0_CTL | Port 0 Control CSR | Section 5.85 |

| 0x1160 | SP1_LM_REQ | Port 1 Link Maintenance Request CSR | Section 5.81 |

| 0x1164 | SP1_LM_RESP | Port 1 Link Maintenance Response CSR | Section 5.82 |

| 0x1168 | SP1_ACKID_STAT | Port 1 Local AckID Status CSR | Section 5.83 |

| 0x1178 | SP1_ERR_STAT | Port 1 Error and Status CSR | Section 5.84 |

| 0x117C | SP1_CTL | Port 1 Control CSR | Section 5.85 |

| 0x1180 | SP2_LM_REQ | Port 2 Link Maintenance Request CSR | Section 5.81 |

| 0x1184 | SP2_LM_RESP | Port 2 Link Maintenance Response CSR | Section 5.82 |

| 0x1188 | SP2_ACKID_STAT | Port 2 Local AckID Status CSR | Section 5.83 |

| 0x1198 | SP2_ERR_STAT | Port 2 Error and Status CSR | Section 5.84 |

| 0x119C | SP2_CTL | Port 2 Control CSR | Section 5.85 |

| 0x11A0 | SP3_LM_REQ | Port 3 Link Maintenance Request CSR | Section 5.81 |

| 0x11A4 | SP3_LM_RESP | Port 3 Link Maintenance Response CSR | Section 5.82 |

| 0x11A8 | SP3_ACKID_STAT | Port 3 Local AckID Status CSR | Section 5.83 |

| 0x11B8 | SP3_ERR_STAT | Port 3 Error and Status CSR | Section 5.84 |

| 0x11BC | SP3_CTL | Port 3 Control CSR | Section 5.85 |

| 0x2000 | ERR_RPT_BH | Error Reporting Block Header | Section 5.86 |

| 0x2008 | ERR_DET | Logical/Transport Layer Error Detect CSR | Section 5.87 |

| 0x200C | ERR_EN | Logical/Transport Layer Error Enable CSR | Section 5.88 |

| 0x2010 | H_ADDR_CAPT | Logical/Transport Layer High Address Capture CSR | Section 5.89 |

| 0x2014 | ADDR_CAPT | Logical/Transport Layer Address Capture CSR | Section 5.90 |

| 0x2018 | ID_CAPT | Logical/Transport Layer Device ID Capture CSR | Section 5.91 |

| 0x201C | CTRL_CAPT | Logical/Transport Layer Control Capture CSR | Section 5.92 |

| 0x2028 | PW_TGT_ID | Section 5.93 | |

| 0x2040 | SP0_ERR_DET | Port 0 Error Detect CSR | Section 5.94 |

| 0x2044 | SP0_RATE_EN | Port 0 Error Enable CSR | Section 5.95 |

96 | Serial RapidIO (SRIO) |

| SPRU976 | |

|

|

|

| Submit Documentation Feedback |