www.ti.com

SRIO Registers

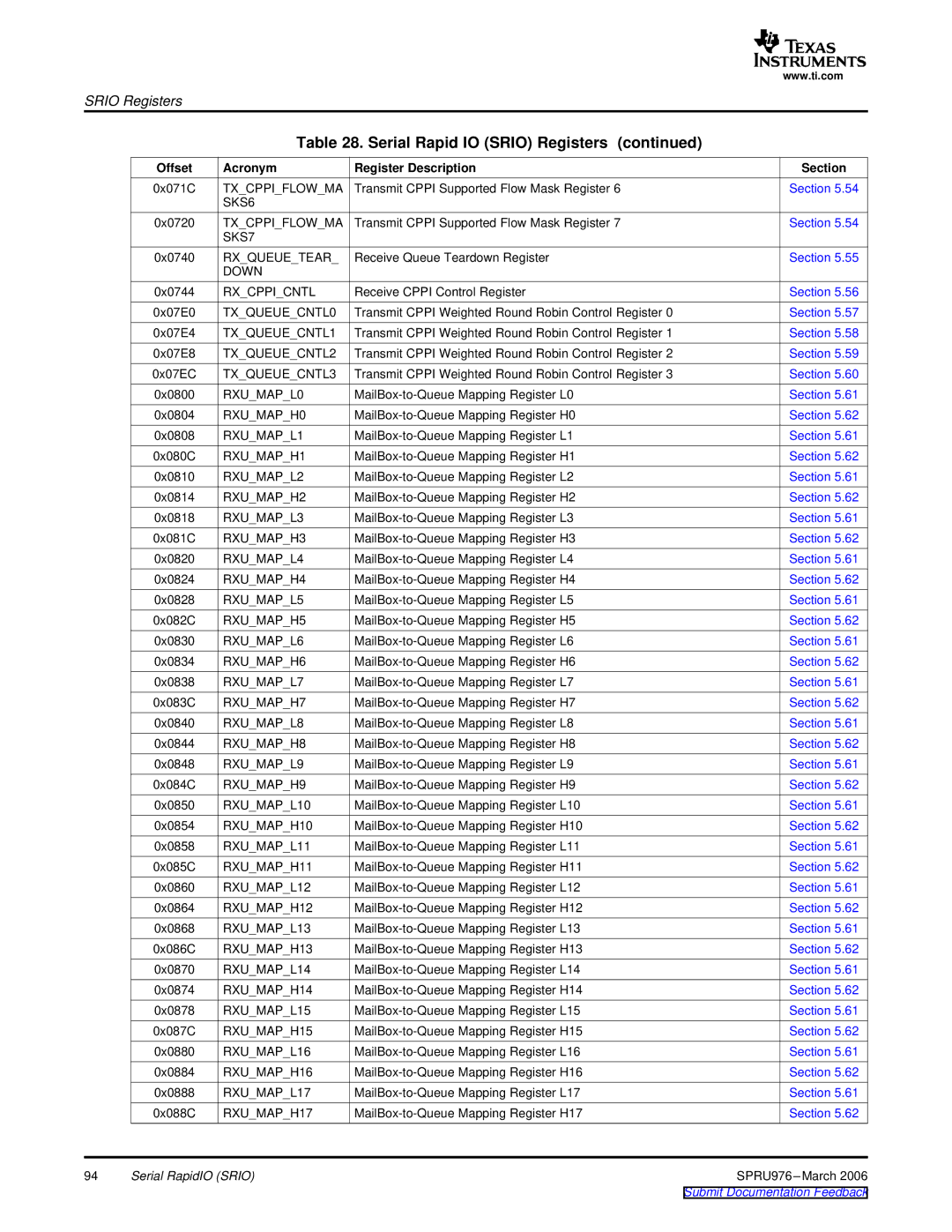

Table 28. Serial Rapid IO (SRIO) Registers (continued)

| Offset | Acronym | Register Description | Section |

| 0x071C | TX_CPPI_FLOW_MA | Transmit CPPI Supported Flow Mask Register 6 | Section 5.54 |

|

| SKS6 |

|

|

| 0x0720 | TX_CPPI_FLOW_MA | Transmit CPPI Supported Flow Mask Register 7 | Section 5.54 |

|

| SKS7 |

|

|

| 0x0740 | RX_QUEUE_TEAR_ | Receive Queue Teardown Register | Section 5.55 |

|

| DOWN |

|

|

| 0x0744 | RX_CPPI_CNTL | Receive CPPI Control Register | Section 5.56 |

| 0x07E0 | TX_QUEUE_CNTL0 | Transmit CPPI Weighted Round Robin Control Register 0 | Section 5.57 |

| 0x07E4 | TX_QUEUE_CNTL1 | Transmit CPPI Weighted Round Robin Control Register 1 | Section 5.58 |

| 0x07E8 | TX_QUEUE_CNTL2 | Transmit CPPI Weighted Round Robin Control Register 2 | Section 5.59 |

| 0x07EC | TX_QUEUE_CNTL3 | Transmit CPPI Weighted Round Robin Control Register 3 | Section 5.60 |

| 0x0800 | RXU_MAP_L0 | Section 5.61 | |

| 0x0804 | RXU_MAP_H0 | Section 5.62 | |

| 0x0808 | RXU_MAP_L1 | Section 5.61 | |

| 0x080C | RXU_MAP_H1 | Section 5.62 | |

| 0x0810 | RXU_MAP_L2 | Section 5.61 | |

| 0x0814 | RXU_MAP_H2 | Section 5.62 | |

| 0x0818 | RXU_MAP_L3 | Section 5.61 | |

| 0x081C | RXU_MAP_H3 | Section 5.62 | |

| 0x0820 | RXU_MAP_L4 | Section 5.61 | |

| 0x0824 | RXU_MAP_H4 | Section 5.62 | |

| 0x0828 | RXU_MAP_L5 | Section 5.61 | |

| 0x082C | RXU_MAP_H5 | Section 5.62 | |

| 0x0830 | RXU_MAP_L6 | Section 5.61 | |

| 0x0834 | RXU_MAP_H6 | Section 5.62 | |

| 0x0838 | RXU_MAP_L7 | Section 5.61 | |

| 0x083C | RXU_MAP_H7 | Section 5.62 | |

| 0x0840 | RXU_MAP_L8 | Section 5.61 | |

| 0x0844 | RXU_MAP_H8 | Section 5.62 | |

| 0x0848 | RXU_MAP_L9 | Section 5.61 | |

| 0x084C | RXU_MAP_H9 | Section 5.62 | |

| 0x0850 | RXU_MAP_L10 | Section 5.61 | |

| 0x0854 | RXU_MAP_H10 | Section 5.62 | |

| 0x0858 | RXU_MAP_L11 | Section 5.61 | |

| 0x085C | RXU_MAP_H11 | Section 5.62 | |

| 0x0860 | RXU_MAP_L12 | Section 5.61 | |

| 0x0864 | RXU_MAP_H12 | Section 5.62 | |

| 0x0868 | RXU_MAP_L13 | Section 5.61 | |

| 0x086C | RXU_MAP_H13 | Section 5.62 | |

| 0x0870 | RXU_MAP_L14 | Section 5.61 | |

| 0x0874 | RXU_MAP_H14 | Section 5.62 | |

| 0x0878 | RXU_MAP_L15 | Section 5.61 | |

| 0x087C | RXU_MAP_H15 | Section 5.62 | |

| 0x0880 | RXU_MAP_L16 | Section 5.61 | |

| 0x0884 | RXU_MAP_H16 | Section 5.62 | |

| 0x0888 | RXU_MAP_L17 | Section 5.61 | |

| 0x088C | RXU_MAP_H17 | Section 5.62 | |

94 | Serial RapidIO (SRIO) |

| SPRU976 | |

|

|

|

| Submit Documentation Feedback |