www.ti.com

SRIO Registers

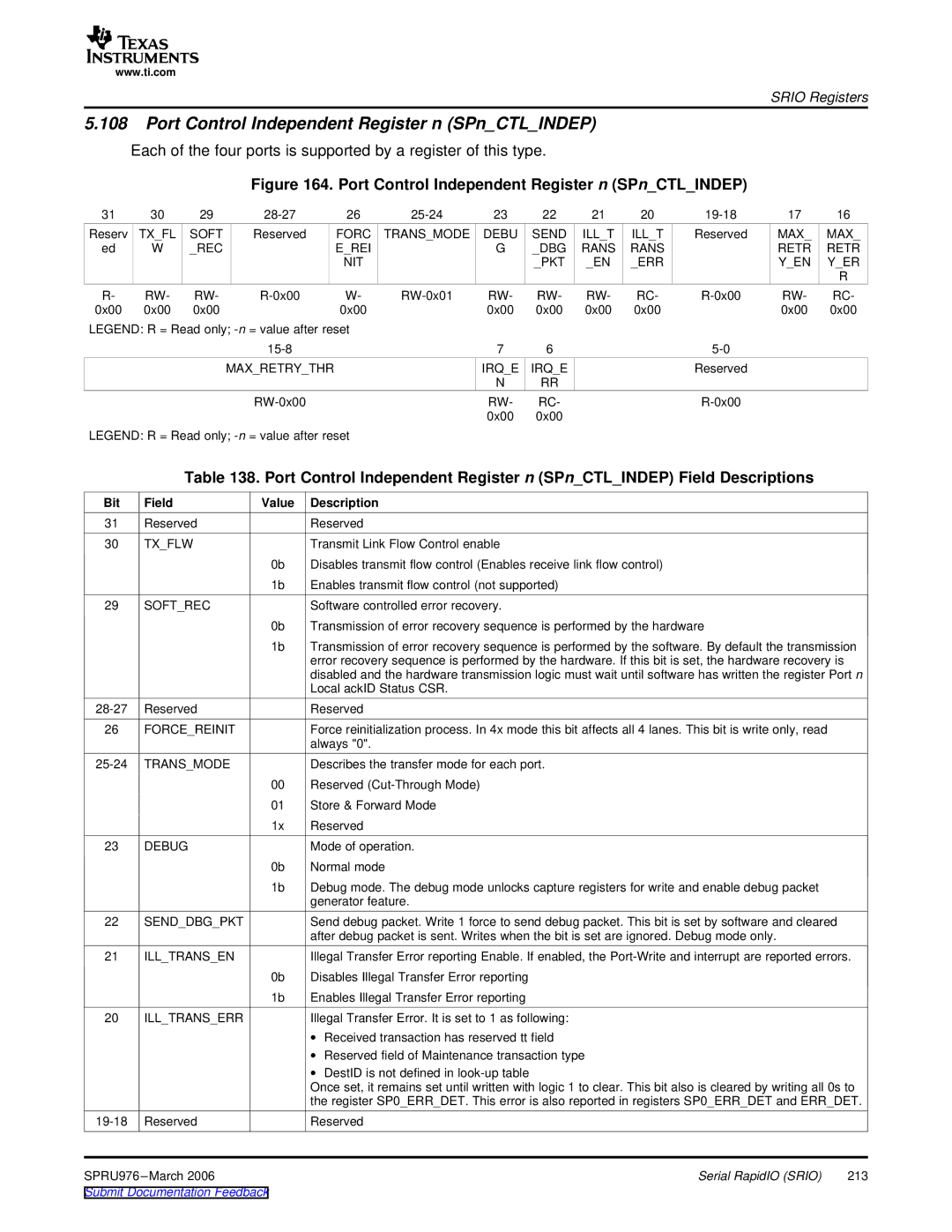

5.108 Port Control Independent Register n (SPn_CTL_INDEP)

Each of the four ports is supported by a register of this type.

Figure 164. Port Control Independent Register n (SPn_CTL_INDEP)

31 | 30 | 29 | 26 | 23 | 22 | 21 | 20 | 17 | 16 | |||

Reserv | TX_FL | SOFT | Reserved | FORC | TRANS_MODE | DEBU | SEND | ILL_T | ILL_T | Reserved | MAX_ | MAX_ |

ed | W | _REC |

| E_REI |

| G | _DBG | RANS | RANS |

| RETR | RETR |

|

|

|

| NIT |

|

| _PKT | _EN | _ERR |

| Y_EN Y_ER | |

|

|

|

|

|

|

|

|

|

|

|

| R |

R- | RW- | RW- | W- | RW- | RW- | RW- | RC- | RW- | RC- | |||

0x00 | 0x00 | 0x00 |

| 0x00 |

| 0x00 | 0x00 | 0x00 | 0x00 |

| 0x00 | 0x00 |

LEGEND: R = Read only; |

|

|

|

|

|

|

|

| ||||

|

|

|

|

| 7 | 6 |

|

|

|

| ||

|

|

| MAX_RETRY_THR |

|

| IRQ_E | IRQ_E |

|

| Reserved |

|

|

|

|

|

|

|

| N | RR |

|

|

|

|

|

|

|

|

|

| RW- | RC- |

|

|

|

| ||

|

|

|

|

|

| 0x00 | 0x00 |

|

|

|

|

|

LEGEND: R = Read only;

Table 138. Port Control Independent Register n (SPn_CTL_INDEP) Field Descriptions

Bit | Field | Value | Description | |

31 | Reserved |

| Reserved | |

30 | TX_FLW |

| Transmit Link Flow Control enable | |

|

| 0b | Disables transmit flow control (Enables receive link flow control) | |

|

| 1b | Enables transmit flow control (not supported) | |

29 | SOFT_REC |

| Software controlled error recovery. | |

|

| 0b | Transmission of error recovery sequence is performed by the hardware | |

|

| 1b | Transmission of error recovery sequence is performed by the software. By default the transmission | |

|

|

| error recovery sequence is performed by the hardware. If this bit is set, the hardware recovery is | |

|

|

| disabled and the hardware transmission logic must wait until software has written the register Port n | |

|

|

| Local ackID Status CSR. | |

Reserved |

| Reserved | ||

26 | FORCE_REINIT |

| Force reinitialization process. In 4x mode this bit affects all 4 lanes. This bit is write only, read | |

|

|

| always "0". | |

| Describes the transfer mode for each port. | |||

|

| 00 | Reserved | |

|

| 01 | Store & Forward Mode | |

|

| 1x | Reserved | |

23 | DEBUG |

| Mode of operation. | |

|

| 0b | Normal mode | |

|

| 1b | Debug mode. The debug mode unlocks capture registers for write and enable debug packet | |

|

|

| generator feature. | |

22 | SEND_DBG_PKT |

| Send debug packet. Write 1 force to send debug packet. This bit is set by software and cleared | |

|

|

| after debug packet is sent. Writes when the bit is set are ignored. Debug mode only. | |

21 | ILL_TRANS_EN |

| Illegal Transfer Error reporting Enable. If enabled, the | |

|

| 0b | Disables Illegal Transfer Error reporting | |

|

| 1b | Enables Illegal Transfer Error reporting | |

20 | ILL_TRANS_ERR |

| Illegal Transfer Error. It is set to 1 as following: | |

|

|

| ∙ | Received transaction has reserved tt field |

|

|

| ∙ | Reserved field of Maintenance transaction type |

|

|

| ∙ | DestID is not defined in |

|

|

| Once set, it remains set until written with logic 1 to clear. This bit also is cleared by writing all 0s to | |

|

|

| the register SP0_ERR_DET. This error is also reported in registers SP0_ERR_DET and ERR_DET. | |

Reserved |

| |

SPRU976 | Serial RapidIO (SRIO) | 213 |

Submit Documentation Feedback |

|

|