www.ti.com

SRIO Registers

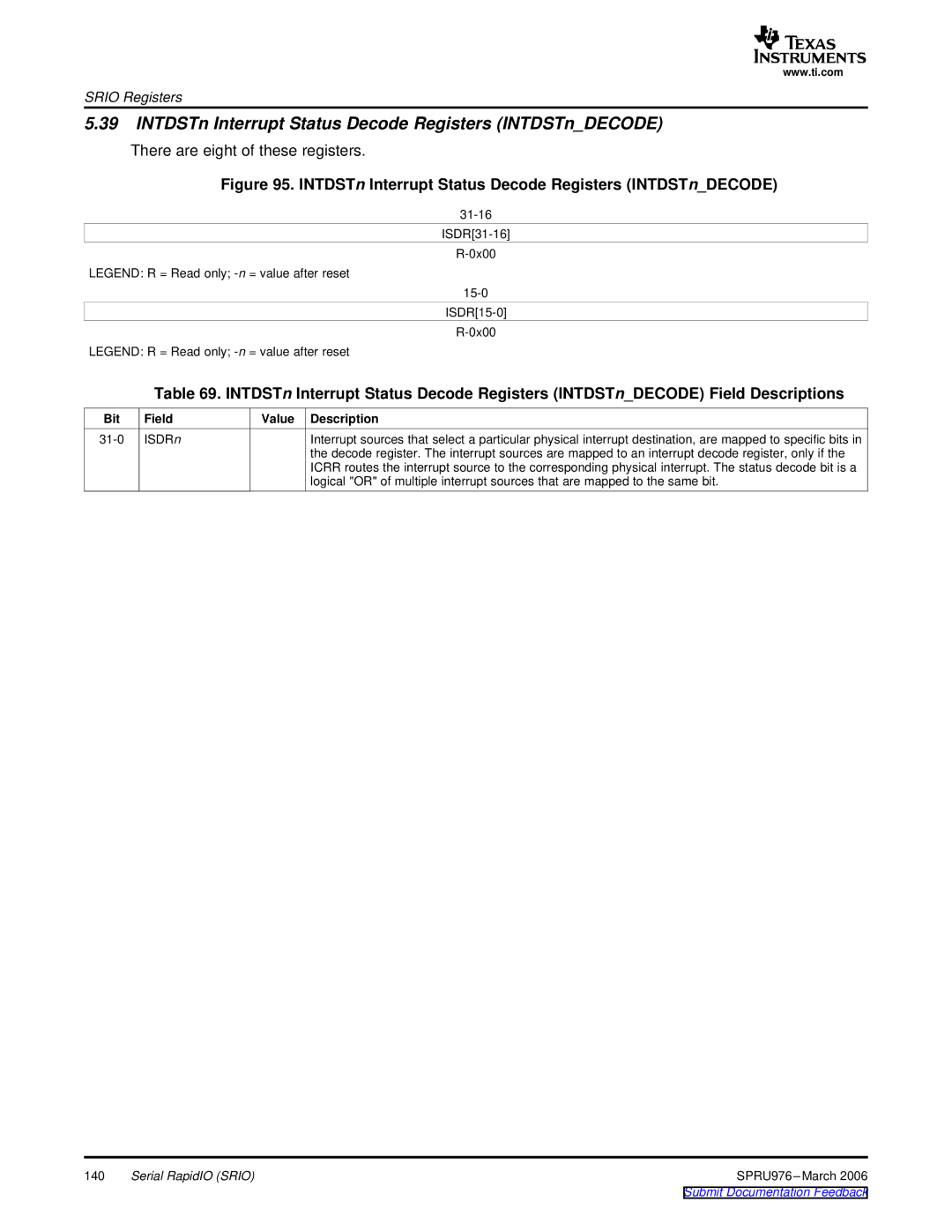

5.39INTDSTn Interrupt Status Decode Registers (INTDSTn_DECODE)

There are eight of these registers.

Figure 95. INTDSTn Interrupt Status Decode Registers (INTDSTn_DECODE)

LEGEND: R = Read only;

LEGEND: R = Read only;

Table 69. INTDSTn Interrupt Status Decode Registers (INTDSTn_DECODE) Field Descriptions

Bit | Field | Value Description |

ISDRn | Interrupt sources that select a particular physical interrupt destination, are mapped to specific bits in | |

|

| the decode register. The interrupt sources are mapped to an interrupt decode register, only if the |

|

| ICRR routes the interrupt source to the corresponding physical interrupt. The status decode bit is a |

|

| logical "OR" of multiple interrupt sources that are mapped to the same bit. |

140 | Serial RapidIO (SRIO) | SPRU976 |