www.ti.com

Overview

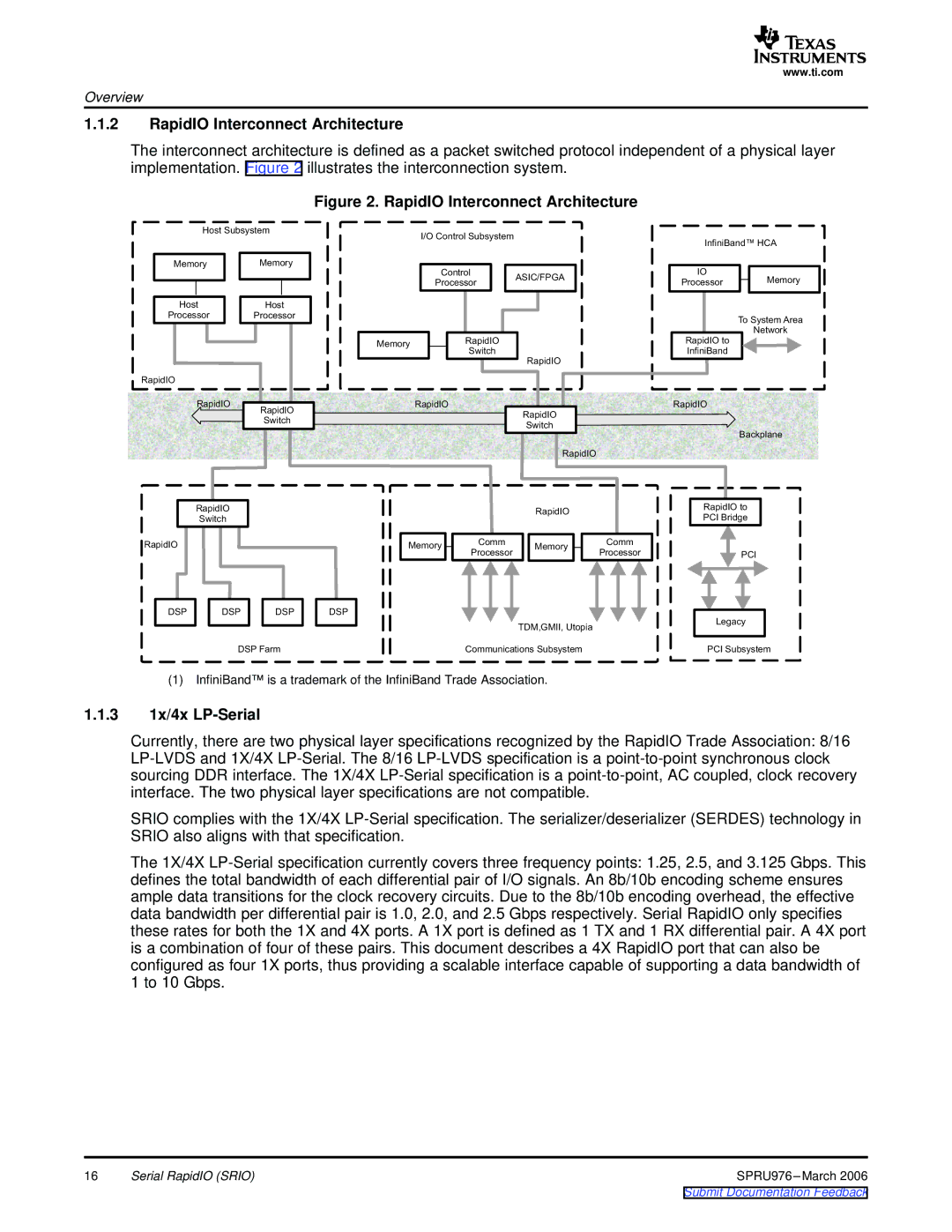

1.1.2RapidIO Interconnect Architecture

The interconnect architecture is defined as a packet switched protocol independent of a physical layer implementation. Figure 2 illustrates the interconnection system.

Figure 2. RapidIO Interconnect Architecture

Host

Memory | Memory |

Host | Host |

Processor | Processor |

RapidIO

RapidIO

RapidIO

Switch

I/O

Control | ASIC/FPGA | |

Processor | ||

|

Memory | RapidIO | |

Switch | ||

| ||

| RapidIO | |

| RapidIO | |

| RapidIO | |

| Switch |

InfiniBand™ HCA | ||

IO | Memory | |

Processor | ||

| ||

To | Area | |

| Network | |

RapidIO |

| |

InfiniBand |

| |

RapidIO

Backplane

RapidIO |

Switch |

RapidIO

DSP | DSP | DSP |

DSP |

|

| RapidIO |

| |

|

| RapidIO |

| |

Memory | Comm | Memory | Comm | |

Processor | Processor | |||

|

| |||

|

| TDM,GMII, |

|

RapidIO |

PCI |

![]() PCI

PCI

Legacy |

DSP Farm | Communications |

PCI

(1)InfiniBand™ is a trademark of the InfiniBand Trade Association.

1.1.31x/4x LP-Serial

Currently, there are two physical layer specifications recognized by the RapidIO Trade Association: 8/16

SRIO complies with the 1X/4X

The 1X/4X

16 | Serial RapidIO (SRIO) | SPRU976 |