www.ti.com

Interrupt Conditions

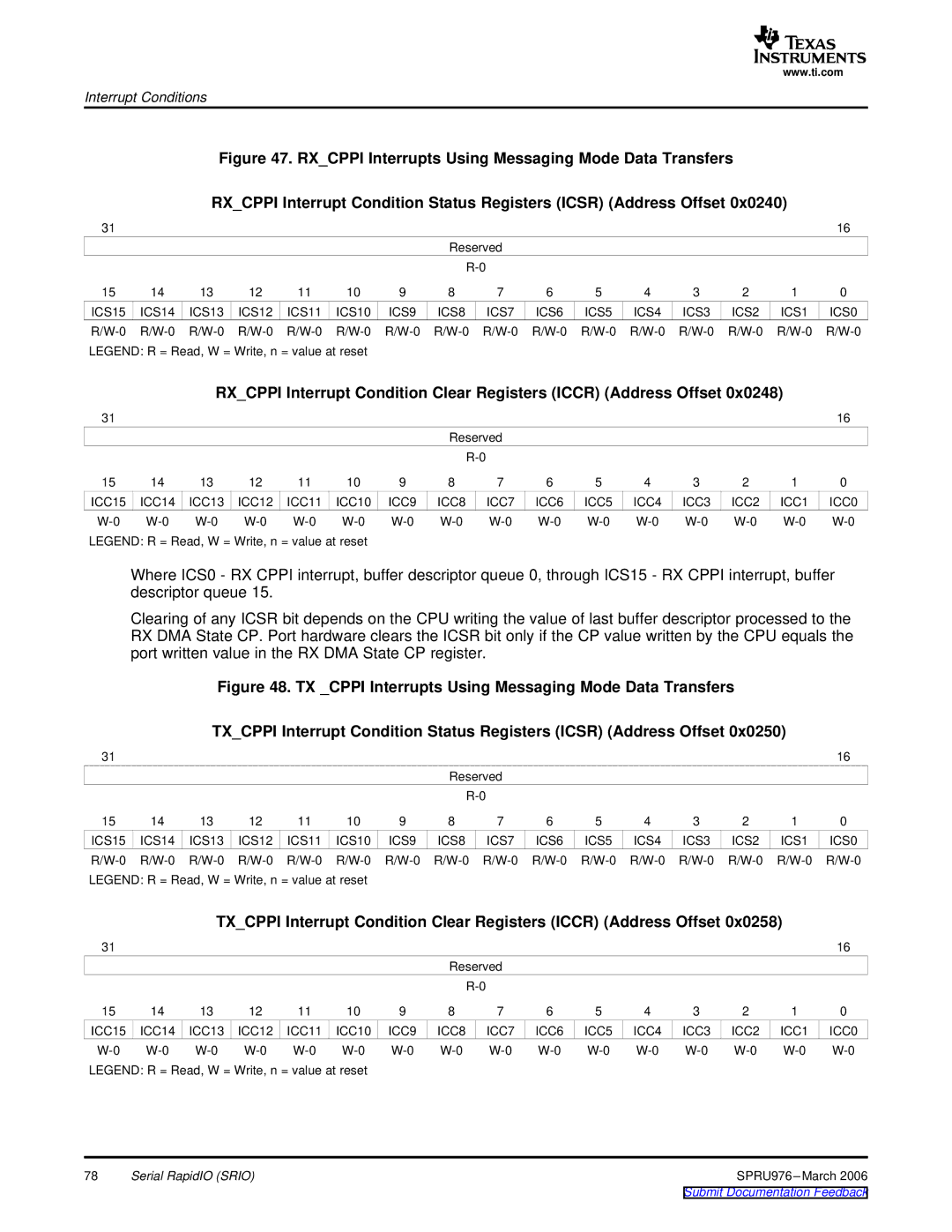

Figure 47. RX_CPPI Interrupts Using Messaging Mode Data Transfers

RX_CPPI Interrupt Condition Status Registers (ICSR) (Address Offset 0x0240)

31 |

|

|

|

|

|

|

|

|

|

|

|

|

|

| 16 |

|

|

|

|

|

|

| Reserved |

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||

15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

ICS15 | ICS14 | ICS13 | ICS12 | ICS11 | ICS10 | ICS9 | ICS8 | ICS7 | ICS6 | ICS5 | ICS4 | ICS3 | ICS2 | ICS1 | ICS0 |

LEGEND: R = Read, W = Write, n = value at reset

RX_CPPI Interrupt Condition Clear Registers (ICCR) (Address Offset 0x0248)

31 |

|

|

|

|

|

|

|

|

|

|

|

|

|

| 16 |

|

|

|

|

|

|

| Reserved |

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |

15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

ICC15 | ICC14 | ICC13 | ICC12 | ICC11 | ICC10 | ICC9 | ICC8 | ICC7 | ICC6 | ICC5 | ICC4 | ICC3 | ICC2 | ICC1 | ICC0 |

LEGEND: R = Read, W = Write, n = value at reset

Where ICS0 - RX CPPI interrupt, buffer descriptor queue 0, through ICS15 - RX CPPI interrupt, buffer descriptor queue 15.

Clearing of any ICSR bit depends on the CPU writing the value of last buffer descriptor processed to the RX DMA State CP. Port hardware clears the ICSR bit only if the CP value written by the CPU equals the port written value in the RX DMA State CP register.

Figure 48. TX _CPPI Interrupts Using Messaging Mode Data Transfers

TX_CPPI Interrupt Condition Status Registers (ICSR) (Address Offset 0x0250)

31 |

|

|

|

|

|

|

|

|

|

|

|

|

|

| 16 |

|

|

|

|

|

|

| Reserved |

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||

15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

ICS15 | ICS14 | ICS13 | ICS12 | ICS11 | ICS10 | ICS9 | ICS8 | ICS7 | ICS6 | ICS5 | ICS4 | ICS3 | ICS2 | ICS1 | ICS0 |

LEGEND: R = Read, W = Write, n = value at reset

TX_CPPI Interrupt Condition Clear Registers (ICCR) (Address Offset 0x0258)

31 |

|

|

|

|

|

|

|

|

|

|

|

|

|

| 16 |

|

|

|

|

|

|

| Reserved |

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |

15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

ICC15 | ICC14 | ICC13 | ICC12 | ICC11 | ICC10 | ICC9 | ICC8 | ICC7 | ICC6 | ICC5 | ICC4 | ICC3 | ICC2 | ICC1 | ICC0 |

LEGEND: R = Read, W = Write, n = value at reset

78 | Serial RapidIO (SRIO) | SPRU976 |

|

| Submit Documentation Feedback |