www.ti.com

SRIO Functional Description

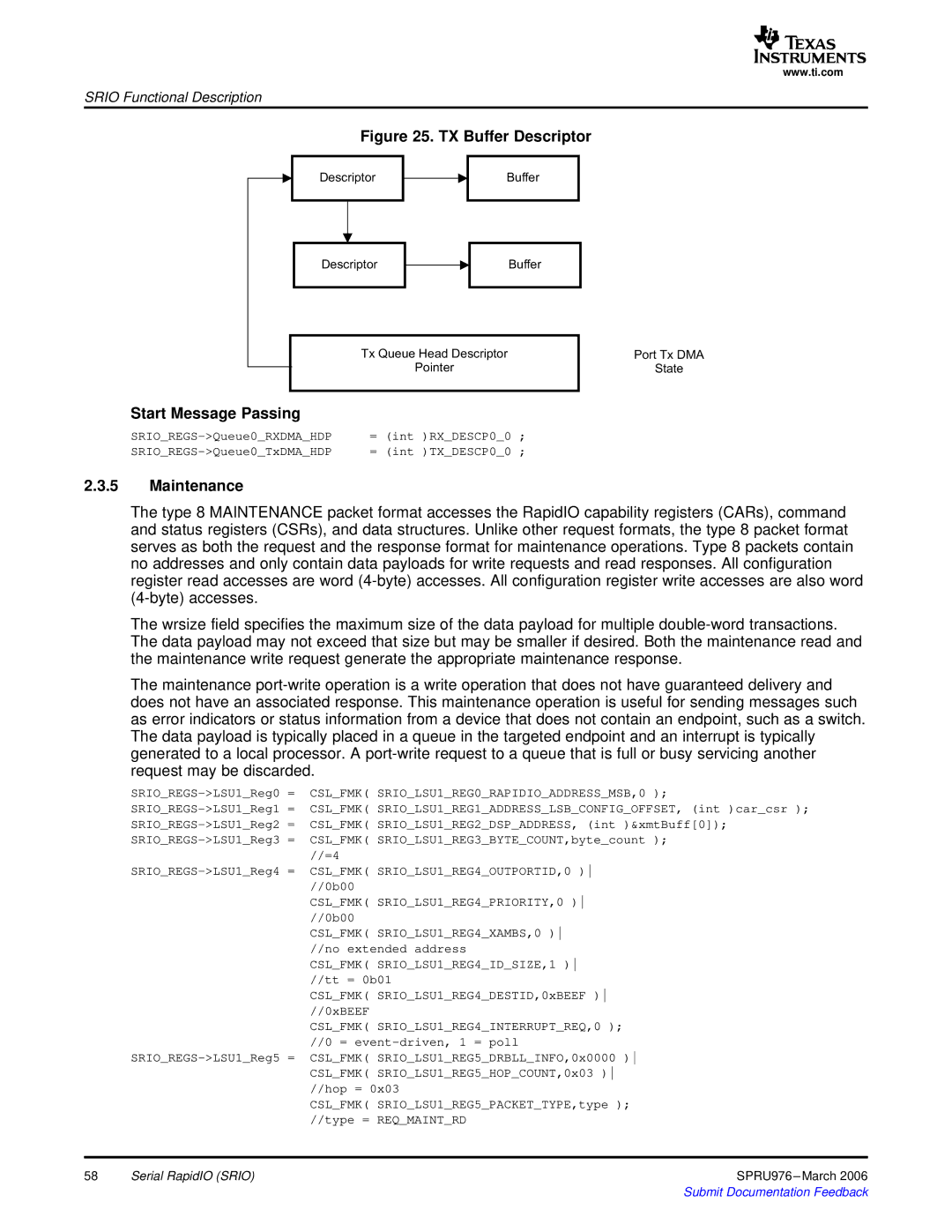

Figure 25. TX Buffer Descriptor

Descriptor

Buffer

Descriptor

Buffer

Tx

Pointer

Start Message Passing

= | (int | )RX_DESCP0_0 | ; | |

= | (int | )TX_DESCP0_0 | ; |

Port Tx State

2.3.5Maintenance

The type 8 MAINTENANCE packet format accesses the RapidIO capability registers (CARs), command and status registers (CSRs), and data structures. Unlike other request formats, the type 8 packet format serves as both the request and the response format for maintenance operations. Type 8 packets contain no addresses and only contain data payloads for write requests and read responses. All configuration register read accesses are word

The wrsize field specifies the maximum size of the data payload for multiple

The maintenance

| CSL_FMK( SRIO_LSU1_REG0_RAPIDIO_ADDRESS_MSB,0 ); | |

| CSL_FMK( SRIO_LSU1_REG1_ADDRESS_LSB_CONFIG_OFFSET, (int )car_csr ); | |

| CSL_FMK( SRIO_LSU1_REG2_DSP_ADDRESS, (int )&xmtBuff[0]); | |

| CSL_FMK( SRIO_LSU1_REG3_BYTE_COUNT,byte_count ); | |

|

| //=4 |

| CSL_FMK( SRIO_LSU1_REG4_OUTPORTID,0 ) | |

|

| //0b00 |

|

| CSL_FMK( SRIO_LSU1_REG4_PRIORITY,0 ) |

|

| //0b00 |

|

| CSL_FMK( SRIO_LSU1_REG4_XAMBS,0 ) |

|

| //no extended address |

|

| CSL_FMK( SRIO_LSU1_REG4_ID_SIZE,1 ) |

|

| //tt = 0b01 |

|

| CSL_FMK( SRIO_LSU1_REG4_DESTID,0xBEEF ) |

|

| //0xBEEF |

|

| CSL_FMK( SRIO_LSU1_REG4_INTERRUPT_REQ,0 ); |

|

| //0 = |

| CSL_FMK( SRIO_LSU1_REG5_DRBLL_INFO,0x0000 ) | |

|

| CSL_FMK( SRIO_LSU1_REG5_HOP_COUNT,0x03 ) |

|

| //hop = 0x03 |

|

| CSL_FMK( SRIO_LSU1_REG5_PACKET_TYPE,type ); |

|

| //type = REQ_MAINT_RD |

58 | Serial RapidIO (SRIO) | SPRU976 |