www.ti.com

SRIO Functional Description

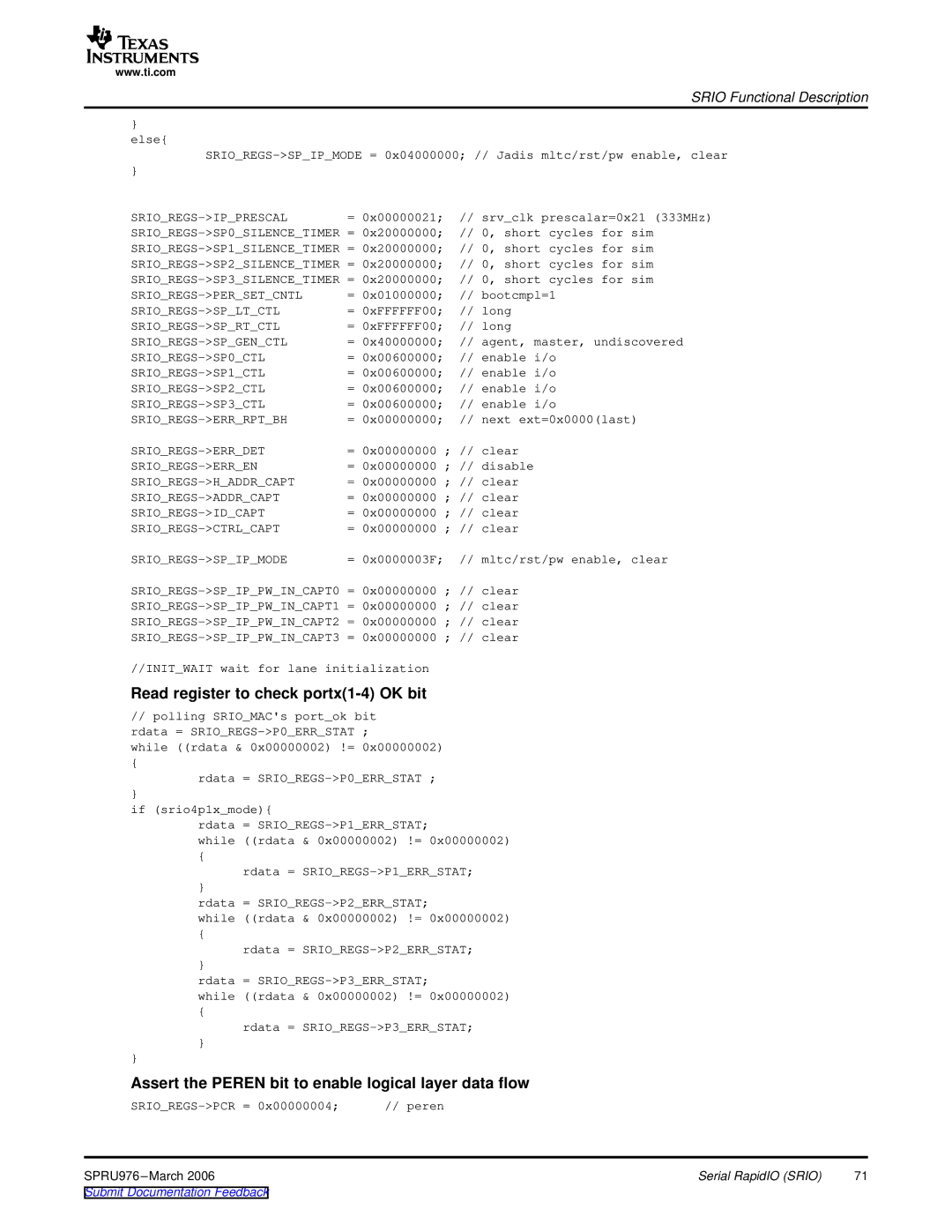

}

else{

} |

|

|

| = 0x00000021; | // srv_clk prescalar=0x21 (333MHz) |

// 0, short cycles for sim | ||

// 0, short cycles for sim | ||

// 0, short cycles for sim | ||

// 0, short cycles for sim | ||

= 0x01000000; | // bootcmpl=1 | |

= 0xFFFFFF00; | // long | |

= 0xFFFFFF00; | // long | |

= 0x40000000; | // agent, master, undiscovered | |

= 0x00600000; | // enable i/o | |

= 0x00600000; | // enable i/o | |

= 0x00600000; | // enable i/o | |

= 0x00600000; | // enable i/o | |

| = 0x00000000; | // next ext=0x0000(last) |

=0x00000000 ; // clear

=0x00000000 ; // disable

=0x00000000 ; // clear

=0x00000000 ; // clear

=0x00000000 ; // clear

=0x00000000 ; // clear

| = 0x0000003F; // mltc/rst/pw enable, clear |

//INIT_WAIT wait for lane initialization

Read register to check portx(1-4) OK bit

//polling SRIO_MAC's port_ok bit rdata =

while ((rdata & 0x00000002) != 0x00000002)

{

rdata =

}

if (srio4p1x_mode){

rdata =

while ((rdata & 0x00000002) != 0x00000002)

{

rdata =

}

rdata =

while ((rdata & 0x00000002) != 0x00000002)

{

rdata =

}

rdata =

while ((rdata & 0x00000002) != 0x00000002)

{

rdata =

}

}

Assert the PEREN bit to enable logical layer data flow

// peren |

| |

SPRU976 | Serial RapidIO (SRIO) | 71 |