www.ti.com

SRIO Functional Description

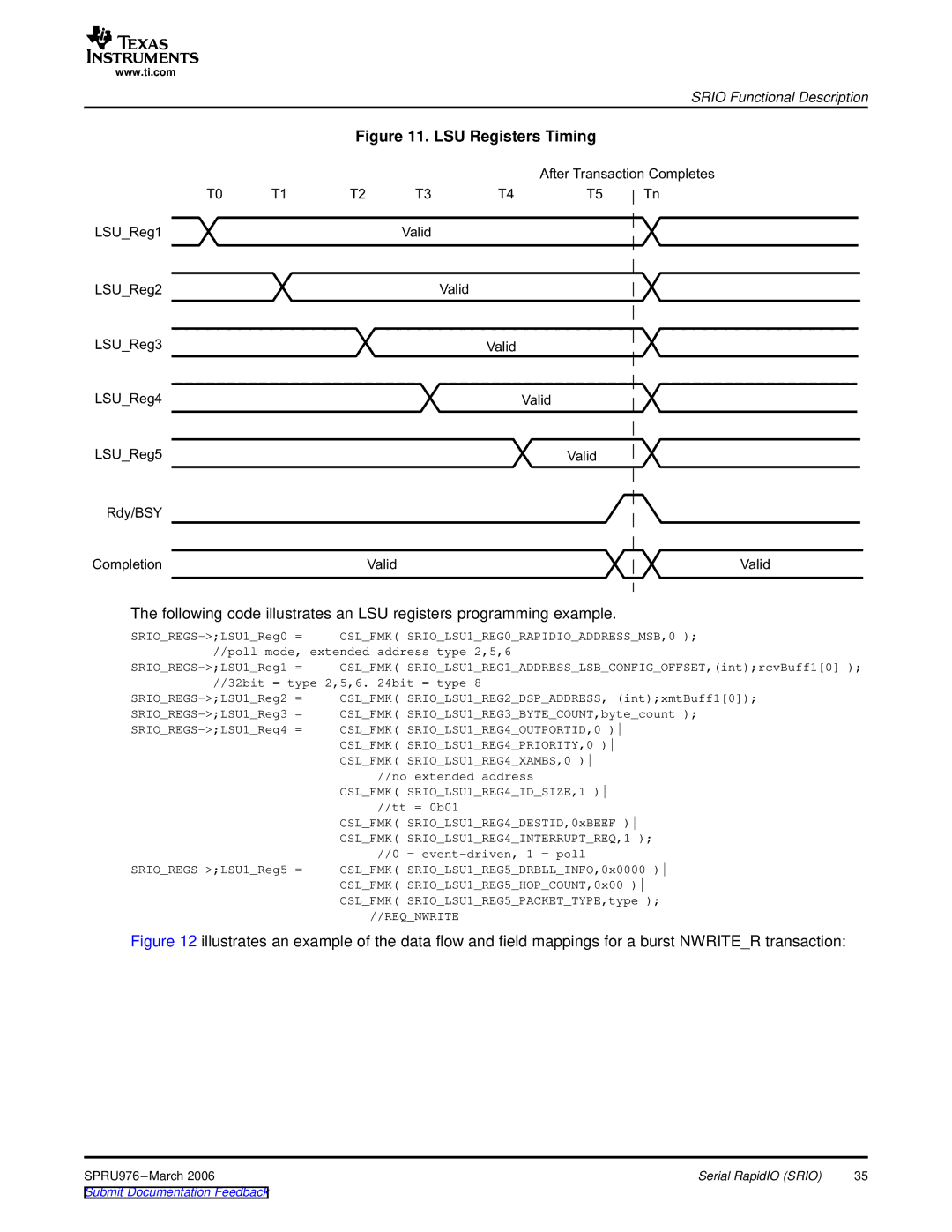

Figure 11. LSU Registers Timing

|

|

|

|

| After Transaction | |

T0 | T1 | T2 | T3 | T4 | T5 | Tn |

LSU_Reg1 |

|

| Valid |

|

|

|

LSU_Reg2 |

|

|

| Valid |

|

|

LSU_Reg3 |

|

|

| Valid |

|

|

LSU_Reg4 |

|

|

|

| Valid |

|

LSU_Reg5 |

|

|

|

| Valid |

|

Rdy/BSY

Completion | Valid | Valid |

The following code illustrates an LSU registers programming example.

CSL_FMK( | SRIO_LSU1_REG0_RAPIDIO_ADDRESS_MSB,0 ); | |

//poll mode, extended address type 2,5,6 | ||

CSL_FMK( | SRIO_LSU1_REG1_ADDRESS_LSB_CONFIG_OFFSET,(int);rcvBuff1[0] ); | |

//32bit = type 2,5,6. 24bit = type 8 | ||

CSL_FMK( | SRIO_LSU1_REG2_DSP_ADDRESS, (int);xmtBuff1[0]); | |

CSL_FMK( | SRIO_LSU1_REG3_BYTE_COUNT,byte_count ); | |

CSL_FMK( | SRIO_LSU1_REG4_OUTPORTID,0 ) | |

| CSL_FMK( | SRIO_LSU1_REG4_PRIORITY,0 ) |

| CSL_FMK( | SRIO_LSU1_REG4_XAMBS,0 ) |

| //no extended address | |

| CSL_FMK( | SRIO_LSU1_REG4_ID_SIZE,1 ) |

| //tt = 0b01 | |

| CSL_FMK( | SRIO_LSU1_REG4_DESTID,0xBEEF ) |

| CSL_FMK( | SRIO_LSU1_REG4_INTERRUPT_REQ,1 ); |

| //0 | = |

CSL_FMK( | SRIO_LSU1_REG5_DRBLL_INFO,0x0000 ) | |

| CSL_FMK( | SRIO_LSU1_REG5_HOP_COUNT,0x00 ) |

| CSL_FMK( | SRIO_LSU1_REG5_PACKET_TYPE,type ); |

//REQ_NWRITE

Figure 12 illustrates an example of the data flow and field mappings for a burst NWRITE_R transaction:

SPRU976 | Serial RapidIO (SRIO) | 35 |