www.ti.com

SRIO Registers

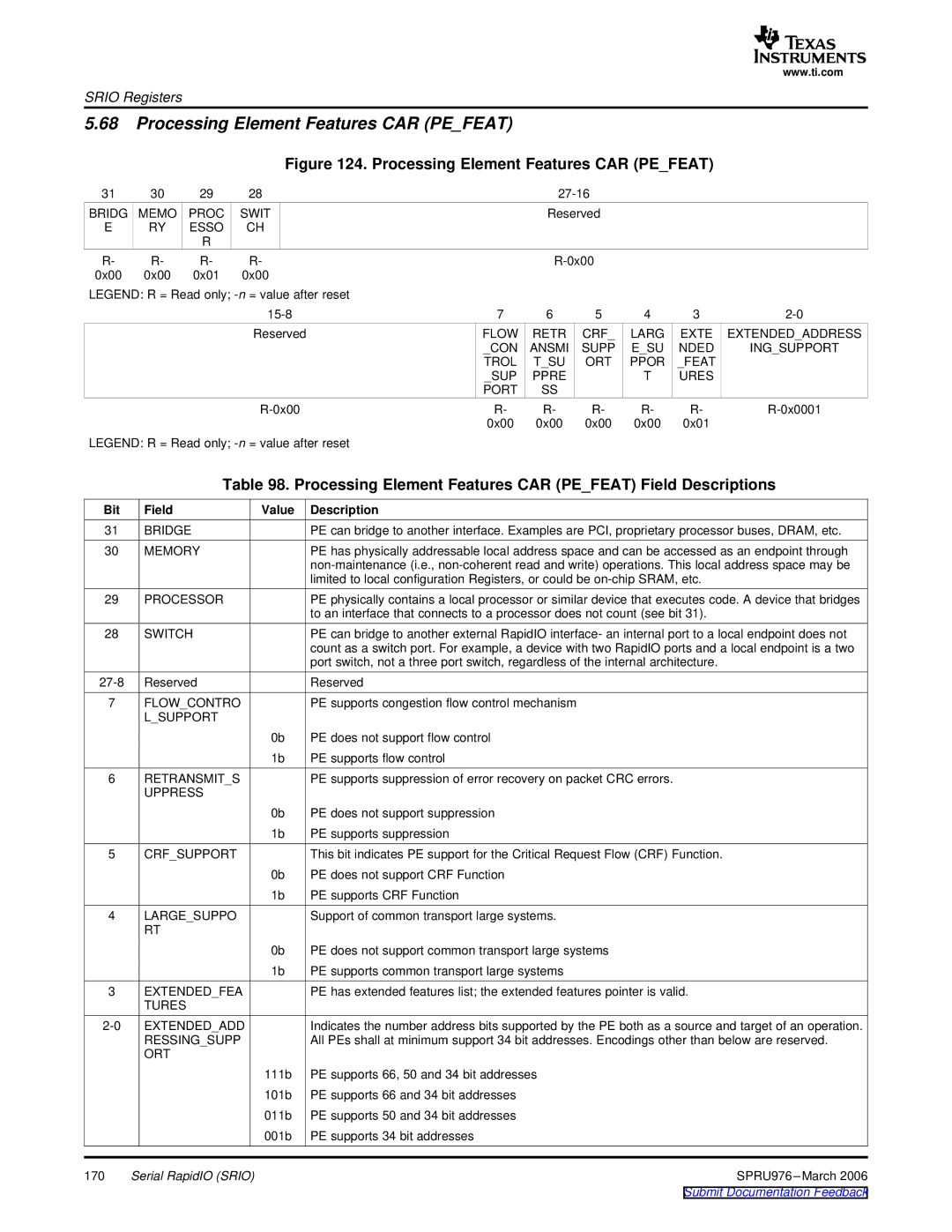

5.68Processing Element Features CAR (PE_FEAT)

|

|

| Figure 124. Processing Element Features CAR (PE_FEAT) |

| |||||

31 | 30 | 29 | 28 |

|

|

|

| ||

BRIDG | MEMO | PROC | SWIT |

| Reserved |

|

|

| |

E | RY | ESSO | CH |

|

|

|

|

|

|

|

| R |

|

|

|

|

|

|

|

R- | R- | R- | R- |

|

|

|

| ||

0x00 | 0x00 | 0x01 | 0x00 |

|

|

|

|

|

|

LEGEND: R = Read only; |

|

|

|

|

|

| |||

|

|

| 7 | 6 | 5 | 4 | 3 | ||

|

|

| Reserved | FLOW | RETR CRF_ LARG EXTE EXTENDED_ADDRESS | ||||

|

|

|

| _CON | ANSMI | SUPP | E_SU | NDED | ING_SUPPORT |

|

|

|

| TROL | T_SU | ORT | PPOR | _FEAT |

|

|

|

|

| _SUP | PPRE |

| T | URES |

|

|

|

|

| PORT | SS |

|

|

|

|

|

|

| R- | R- | R- | R- | R- | ||

|

|

|

| 0x00 | 0x00 | 0x00 | 0x00 | 0x01 |

|

LEGEND: R = Read only;

Table 98. Processing Element Features CAR (PE_FEAT) Field Descriptions

Bit | Field | Value | Description |

31 | BRIDGE |

| PE can bridge to another interface. Examples are PCI, proprietary processor buses, DRAM, etc. |

30 | MEMORY |

| PE has physically addressable local address space and can be accessed as an endpoint through |

|

|

| |

|

|

| limited to local configuration Registers, or could be |

29 | PROCESSOR |

| PE physically contains a local processor or similar device that executes code. A device that bridges |

|

|

| to an interface that connects to a processor does not count (see bit 31). |

28 | SWITCH |

| PE can bridge to another external RapidIO interface- an internal port to a local endpoint does not |

|

|

| count as a switch port. For example, a device with two RapidIO ports and a local endpoint is a two |

|

|

| port switch, not a three port switch, regardless of the internal architecture. |

Reserved |

| Reserved | |

7 | FLOW_CONTRO |

| PE supports congestion flow control mechanism |

| L_SUPPORT |

|

|

|

| 0b | PE does not support flow control |

|

| 1b | PE supports flow control |

6 | RETRANSMIT_S |

| PE supports suppression of error recovery on packet CRC errors. |

| UPPRESS |

|

|

|

| 0b | PE does not support suppression |

|

| 1b | PE supports suppression |

5 | CRF_SUPPORT |

| This bit indicates PE support for the Critical Request Flow (CRF) Function. |

|

| 0b | PE does not support CRF Function |

|

| 1b | PE supports CRF Function |

4 | LARGE_SUPPO |

| Support of common transport large systems. |

| RT |

|

|

|

| 0b | PE does not support common transport large systems |

|

| 1b | PE supports common transport large systems |

3 | EXTENDED_FEA |

| PE has extended features list; the extended features pointer is valid. |

| TURES |

|

|

EXTENDED_ADD |

| Indicates the number address bits supported by the PE both as a source and target of an operation. | |

| RESSING_SUPP |

| All PEs shall at minimum support 34 bit addresses. Encodings other than below are reserved. |

| ORT |

|

|

|

| 111b | PE supports 66, 50 and 34 bit addresses |

|

| 101b | PE supports 66 and 34 bit addresses |

|

| 011b | PE supports 50 and 34 bit addresses |

|

| 001b | PE supports 34 bit addresses |

170 | Serial RapidIO (SRIO) |

| SPRU976 |