www.ti.com

Overview

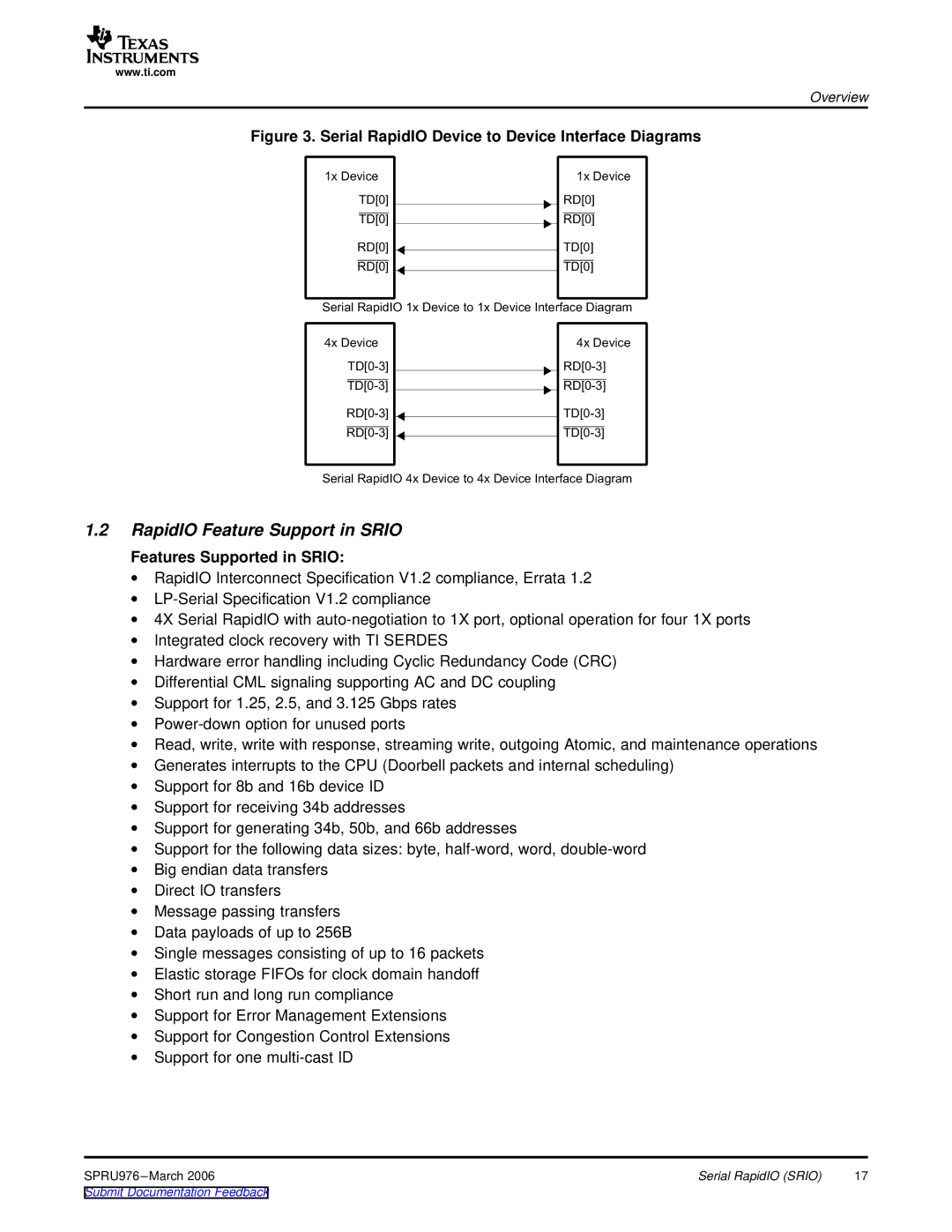

Figure 3. Serial RapidIO Device to Device Interface Diagrams

1x

TD[0]

TD[0]

RD[0]

RD[0]

Serial

4x

1x

RD[0]

RD[0]

TD[0]

TD[0]

4x

Serial

1.2RapidIO Feature Support in SRIO

Features Supported in SRIO:

∙RapidIO Interconnect Specification V1.2 compliance, Errata 1.2

∙

∙4X Serial RapidIO with

∙Integrated clock recovery with TI SERDES

∙Hardware error handling including Cyclic Redundancy Code (CRC)

∙Differential CML signaling supporting AC and DC coupling

∙Support for 1.25, 2.5, and 3.125 Gbps rates

∙

∙Read, write, write with response, streaming write, outgoing Atomic, and maintenance operations

∙Generates interrupts to the CPU (Doorbell packets and internal scheduling)

∙Support for 8b and 16b device ID

∙Support for receiving 34b addresses

∙Support for generating 34b, 50b, and 66b addresses

∙Support for the following data sizes: byte,

∙Big endian data transfers

∙Direct IO transfers

∙Message passing transfers

∙Data payloads of up to 256B

∙Single messages consisting of up to 16 packets

∙Elastic storage FIFOs for clock domain handoff

∙Short run and long run compliance

∙Support for Error Management Extensions

∙Support for Congestion Control Extensions

∙Support for one

SPRU976 | Serial RapidIO (SRIO) | 17 |