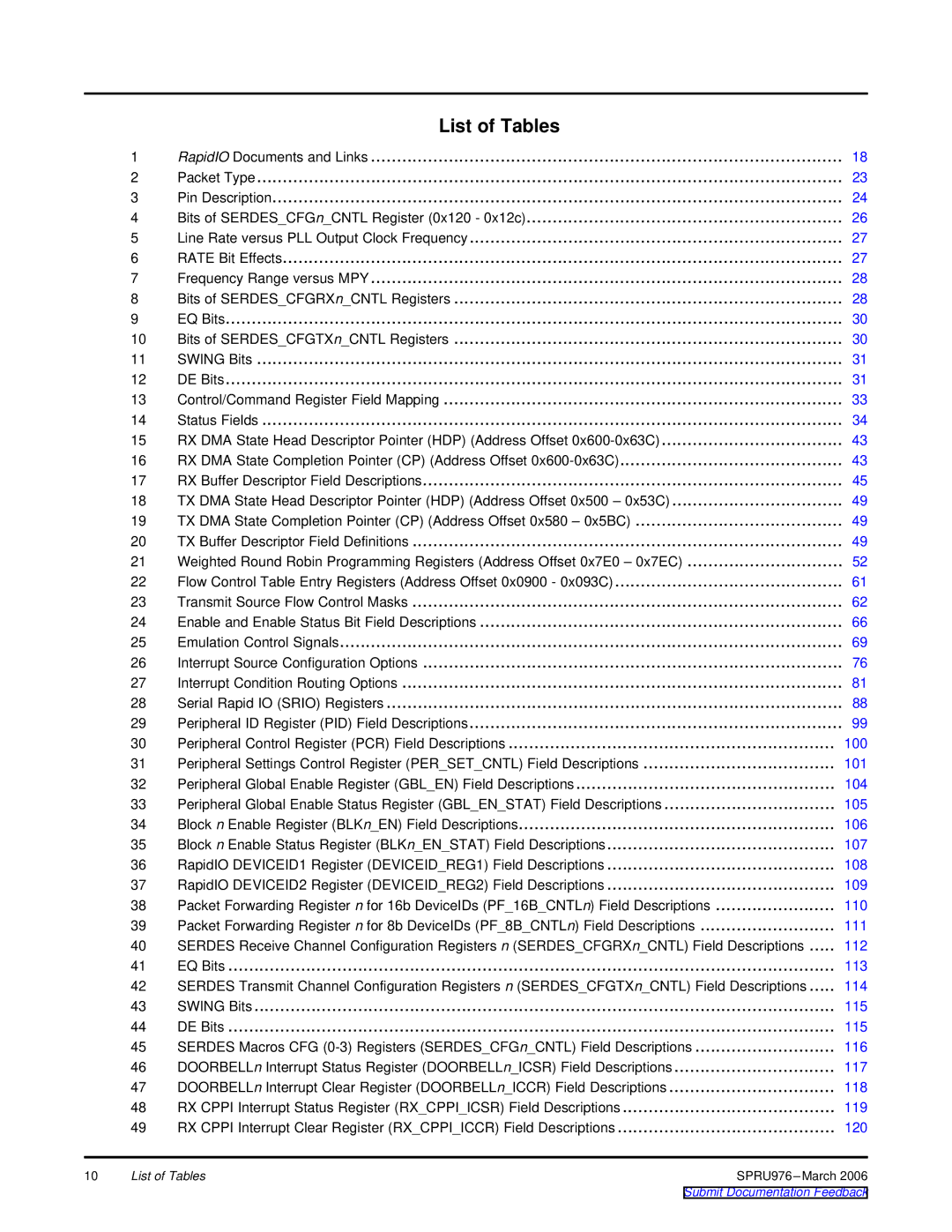

List of Tables

| 1 | RapidIO Documents and Links | 18 | |

| 2 | Packet Type | 23 | |

| 3 | Pin Description | 24 | |

| 4 | Bits of SERDES_CFGn_CNTL Register (0x120 - 0x12c) | 26 | |

| 5 | Line Rate versus PLL Output Clock Frequency | 27 | |

| 6 | RATE Bit Effects | 27 | |

| 7 | Frequency Range versus MPY | 28 | |

| 8 | Bits of SERDES_CFGRXn_CNTL Registers | 28 | |

| 9 | EQ Bits | 30 | |

| 10 | Bits of SERDES_CFGTXn_CNTL Registers | 30 | |

| 11 | SWING Bits | 31 | |

| 12 | DE Bits | 31 | |

| 13 | Control/Command Register Field Mapping | 33 | |

| 14 | Status Fields | 34 | |

| 15 | RX DMA State Head Descriptor Pointer (HDP) (Address Offset | 43 | |

| 16 | RX DMA State Completion Pointer (CP) (Address Offset | 43 | |

| 17 | RX Buffer Descriptor Field Descriptions | 45 | |

| 18 | TX DMA State Head Descriptor Pointer (HDP) (Address Offset 0x500 – 0x53C) | 49 | |

| 19 | TX DMA State Completion Pointer (CP) (Address Offset 0x580 – 0x5BC) | 49 | |

| 20 | TX Buffer Descriptor Field Definitions | 49 | |

| 21 | Weighted Round Robin Programming Registers (Address Offset 0x7E0 – 0x7EC) | 52 | |

| 22 | Flow Control Table Entry Registers (Address Offset 0x0900 - 0x093C) | 61 | |

| 23 | Transmit Source Flow Control Masks | 62 | |

| 24 | Enable and Enable Status Bit Field Descriptions | 66 | |

| 25 | Emulation Control Signals | 69 | |

| 26 | Interrupt Source Configuration Options | 76 | |

| 27 | Interrupt Condition Routing Options | 81 | |

| 28 | Serial Rapid IO (SRIO) Registers | 88 | |

| 29 | Peripheral ID Register (PID) Field Descriptions | 99 | |

| 30 | Peripheral Control Register (PCR) Field Descriptions | 100 | |

| 31 | Peripheral Settings Control Register (PER_SET_CNTL) Field Descriptions | 101 | |

| 32 | Peripheral Global Enable Register (GBL_EN) Field Descriptions | 104 | |

| 33 | Peripheral Global Enable Status Register (GBL_EN_STAT) Field Descriptions | 105 | |

| 34 | Block n Enable Register (BLKn_EN) Field Descriptions | 106 | |

| 35 | Block n Enable Status Register (BLKn_EN_STAT) Field Descriptions | 107 | |

| 36 | RapidIO DEVICEID1 Register (DEVICEID_REG1) Field Descriptions | 108 | |

| 37 | RapidIO DEVICEID2 Register (DEVICEID_REG2) Field Descriptions | 109 | |

| 38 | Packet Forwarding Register n for 16b DeviceIDs (PF_16B_CNTLn) Field Descriptions | 110 | |

| 39 | Packet Forwarding Register n for 8b DeviceIDs (PF_8B_CNTLn) Field Descriptions | 111 | |

| 40 | SERDES Receive Channel Configuration Registers n (SERDES_CFGRXn_CNTL) Field Descriptions | 112 | |

| 41 | EQ Bits | 113 | |

| 42 | SERDES Transmit Channel Configuration Registers n (SERDES_CFGTXn_CNTL) Field Descriptions | 114 | |

| 43 | SWING Bits | 115 | |

| 44 | DE Bits | 115 | |

| 45 | SERDES Macros CFG | 116 | |

| 46 | DOORBELLn Interrupt Status Register (DOORBELLn_ICSR) Field Descriptions | 117 | |

| 47 | DOORBELLn Interrupt Clear Register (DOORBELLn_ICCR) Field Descriptions | 118 | |

| 48 | RX CPPI Interrupt Status Register (RX_CPPI_ICSR) Field Descriptions | 119 | |

| 49 | RX CPPI Interrupt Clear Register (RX_CPPI_ICCR) Field Descriptions | 120 | |

10 | List of Tables | SPRU976 | ||