www.ti.com

SRIO Registers

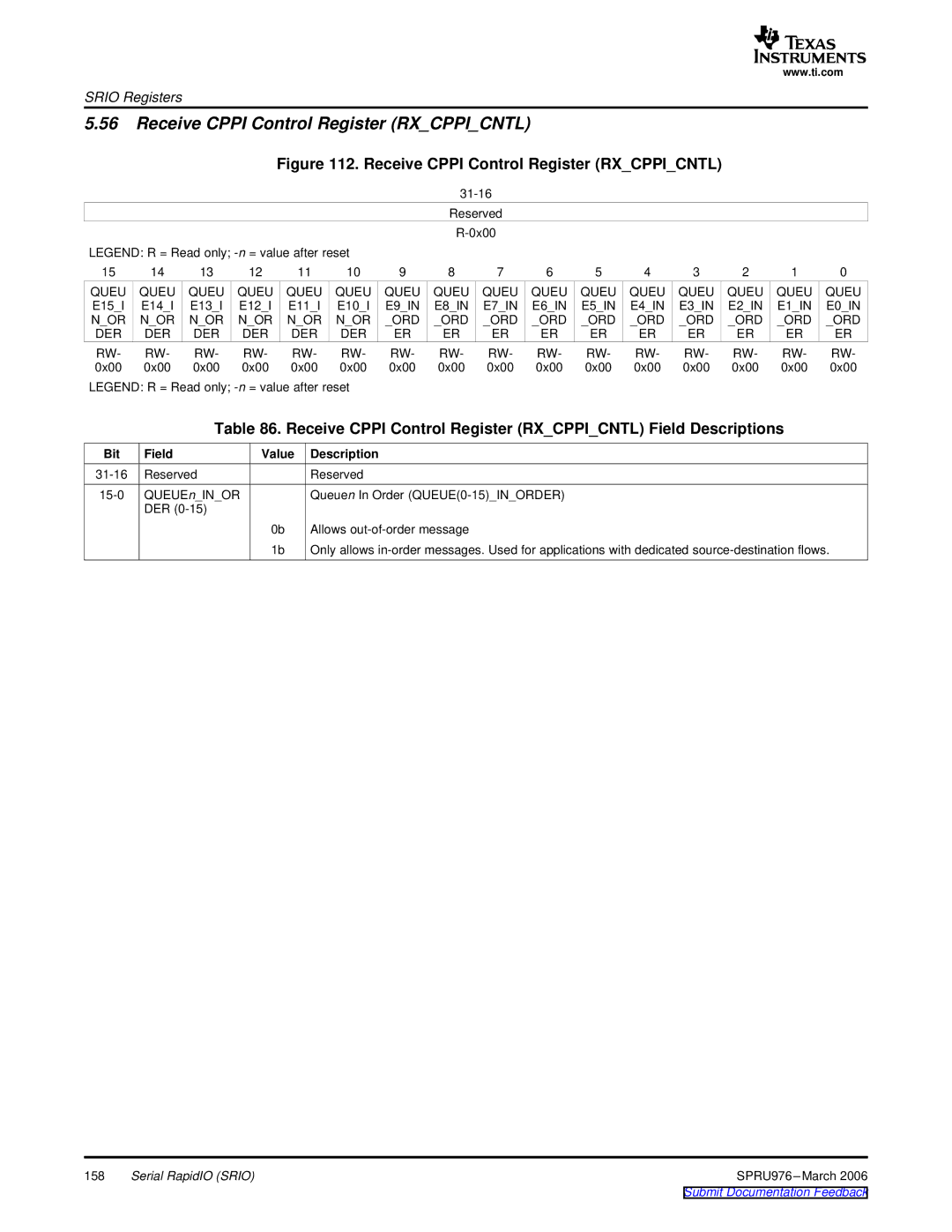

5.56Receive CPPI Control Register (RX_CPPI_CNTL)

Figure 112. Receive CPPI Control Register (RX_CPPI_CNTL)

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||

|

|

|

|

|

|

| Reserved |

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||

LEGEND: R = Read only; |

|

|

|

|

|

|

|

|

|

| |||||

15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

QUEU QUEU QUEU QUEU QUEU QUEU | QUEU | QUEU | QUEU | QUEU | QUEU | QUEU | QUEU | QUEU | QUEU | QUEU | |||||

E15_I | E14_I | E13_I | E12_I | E11_I | E10_I | E9_IN | E8_IN | E7_IN | E6_IN | E5_IN | E4_IN | E3_IN | E2_IN | E1_IN | E0_IN |

N_OR | N_OR N_OR N_OR N_OR N_OR | _ORD | _ORD | _ORD | _ORD | _ORD | _ORD | _ORD | _ORD _ORD _ORD | ||||||

DER | DER | DER | DER | DER | DER | ER | ER | ER | ER | ER | ER | ER | ER | ER | ER |

RW- | RW- | RW- | RW- | RW- | RW- | RW- | RW- | RW- | RW- | RW- | RW- | RW- | RW- | RW- | RW- |

0x00 | 0x00 | 0x00 | 0x00 | 0x00 | 0x00 | 0x00 | 0x00 | 0x00 | 0x00 | 0x00 | 0x00 | 0x00 | 0x00 | 0x00 | 0x00 |

LEGEND: R = Read only;

Table 86. Receive CPPI Control Register (RX_CPPI_CNTL) Field Descriptions

Bit | Field | Value | Description |

Reserved |

| Reserved | |

QUEUEn_IN_OR |

| Queuen In Order | |

| DER |

|

|

|

| 0b | Allows |

|

| 1b | Only allows |

158 | Serial RapidIO (SRIO) | SPRU976 |