www.ti.com

SRIO Functional Description

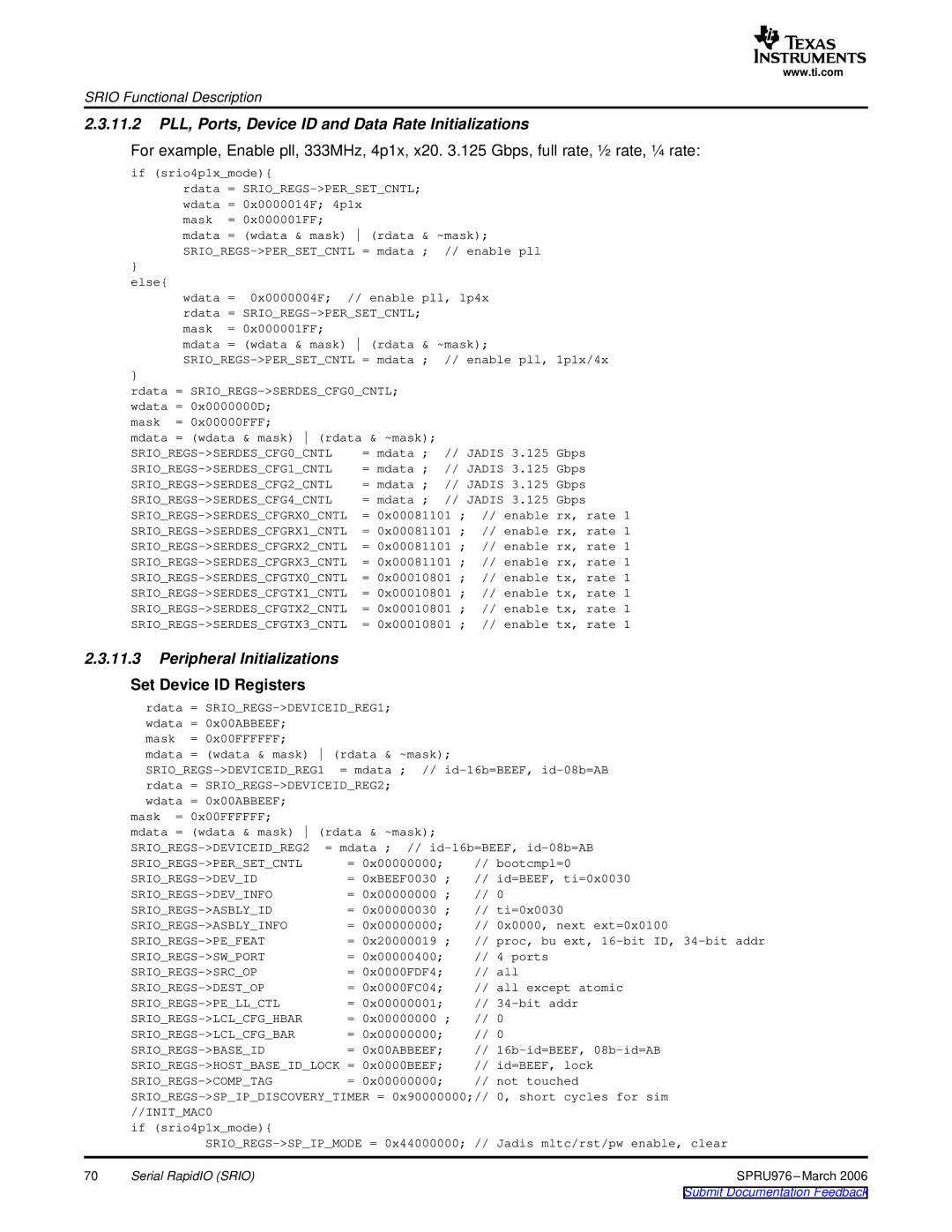

2.3.11.2PLL, Ports, Device ID and Data Rate Initializations

For example, Enable pll, 333MHz, 4p1x, x20. 3.125 Gbps, full rate, ½ rate, ¼ rate:

if (srio4p1x_mode){ |

|

|

|

| ||

| rdata = |

|

|

| ||

| wdata = 0x0000014F; 4p1x |

|

|

|

| |

| mask | = 0x000001FF; |

|

|

|

|

| mdata = (wdata & mask) (rdata & ~mask); |

| ||||

| = mdata ; | // enable pll |

| |||

} |

|

|

|

|

|

|

else{ |

|

|

|

|

|

|

| wdata = 0x0000004F; // enable pll, 1p4x |

| ||||

| rdata = |

|

|

| ||

| mask | = 0x000001FF; |

|

|

|

|

| mdata = (wdata & mask) (rdata & ~mask); |

| ||||

| = mdata ; | // enable pll, | 1p1x/4x | |||

} |

|

|

|

|

|

|

rdata = |

|

|

| |||

wdata | = 0x0000000D; |

|

|

|

| |

mask | = 0x00000FFF; |

|

|

|

| |

mdata = (wdata & mask) (rdata & ~mask); |

|

|

| |||

= mdata ; | // JADIS 3.125 | Gbps | ||||

= mdata ; | // JADIS 3.125 | Gbps | ||||

= mdata ; | // JADIS 3.125 | Gbps | ||||

| = mdata ; | // JADIS 3.125 | Gbps | |||

= 0x00081101 ; | // enable | rx, rate 1 | ||||

= 0x00081101 ; | // enable | rx, rate 1 | ||||

= 0x00081101 ; | // enable | rx, rate 1 | ||||

= 0x00081101 ; | // enable | rx, rate 1 | ||||

= 0x00010801 ; | // enable | tx, rate 1 | ||||

= 0x00010801 ; | // enable | tx, rate 1 | ||||

= 0x00010801 ; | // enable | tx, rate 1 | ||||

= 0x00010801 ; | // enable | tx, rate 1 | ||||

2.3.11.3Peripheral Initializations

Set Device ID Registers

| rdata = |

|

| |||

| wdata | = 0x00ABBEEF; |

|

|

|

|

| mask | = 0x00FFFFFF; |

|

|

|

|

| mdata = (wdata & mask) (rdata & ~mask); |

|

| |||

| = mdata ; // | |||||

| rdata = |

|

| |||

| wdata = 0x00ABBEEF; |

|

|

|

| |

| mask = 0x00FFFFFF; |

|

|

|

| |

| mdata = (wdata & mask) (rdata & ~mask); |

|

| |||

| = mdata ; // | |||||

| = | 0x00000000; | // | bootcmpl=0 | ||

| = | 0xBEEF0030 ; | // | id=BEEF, ti=0x0030 | ||

| = | 0x00000000 ; | // | 0 | ||

| = | 0x00000030 ; | // | ti=0x0030 | ||

| = | 0x00000000; | // | 0x0000, next ext=0x0100 | ||

| = | 0x20000019 ; | // | proc, bu ext, | ||

| = | 0x00000400; | // | 4 ports | ||

| = | 0x0000FDF4; | // | all | ||

| = | 0x0000FC04; | // | all except atomic | ||

| = | 0x00000001; | // | |||

| = | 0x00000000 ; | // | 0 | ||

| = | 0x00000000; | // | 0 | ||

| = | 0x00ABBEEF; | // | |||

| 0x0000BEEF; | // | id=BEEF, lock | |||

| = | 0x00000000; | // | not touched | ||

| 0, short cycles for sim | |||||

| //INIT_MAC0 |

|

|

|

| |

| if (srio4p1x_mode){ |

|

|

|

| |

|

| Jadis mltc/rst/pw enable, clear | ||||

70 | Serial RapidIO (SRIO) |

|

|

| SPRU976 | |