www.ti.com

SRIO Functional Description

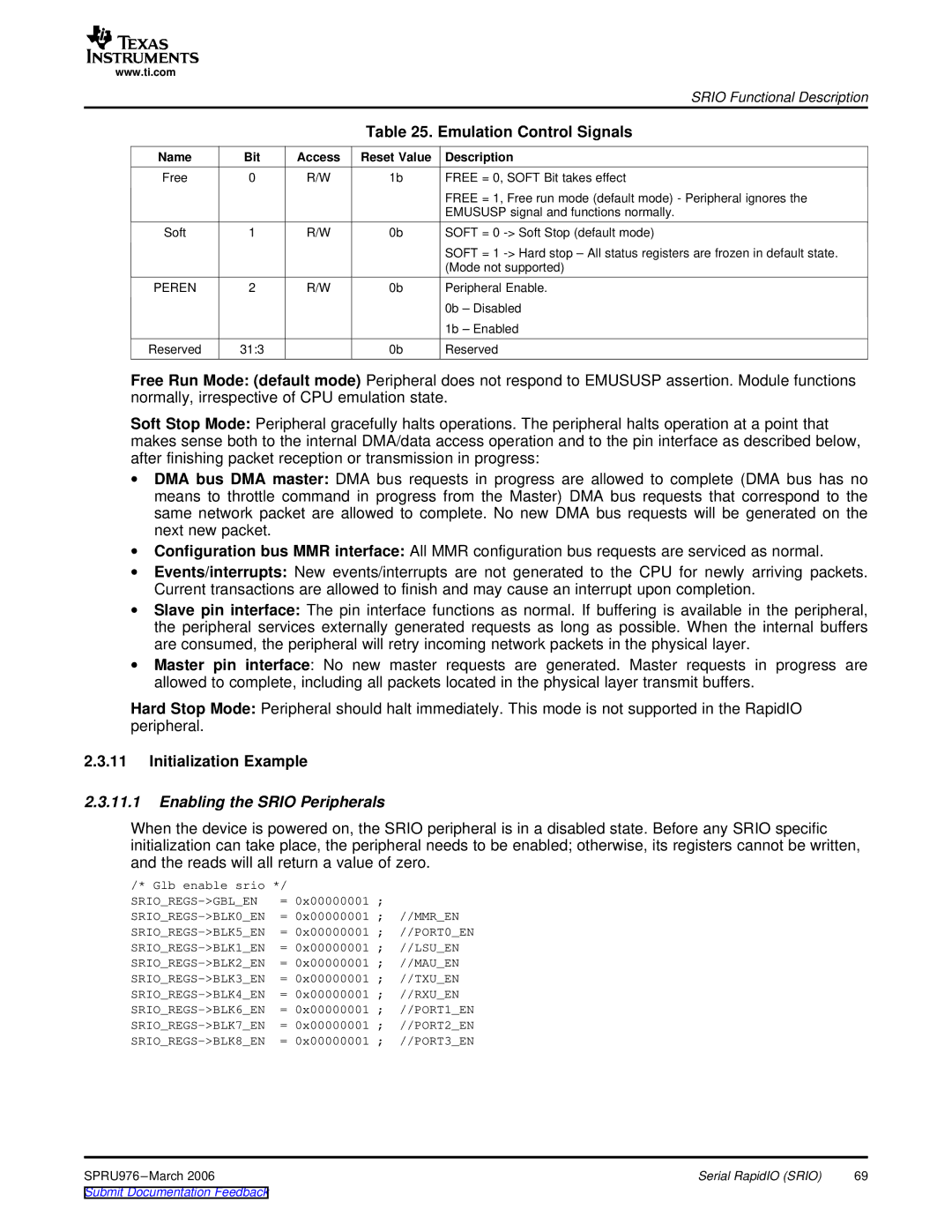

Table 25. Emulation Control Signals

Name | Bit | Access | Reset Value | Description |

Free | 0 | R/W | 1b | FREE = 0, SOFT Bit takes effect |

|

|

|

| FREE = 1, Free run mode (default mode) - Peripheral ignores the |

|

|

|

| EMUSUSP signal and functions normally. |

Soft | 1 | R/W | 0b | SOFT = 0 |

|

|

|

| SOFT = 1 |

|

|

|

| (Mode not supported) |

PEREN | 2 | R/W | 0b | Peripheral Enable. |

|

|

|

| 0b – Disabled |

|

|

|

| 1b – Enabled |

Reserved | 31:3 |

| 0b | Reserved |

Free Run Mode: (default mode) Peripheral does not respond to EMUSUSP assertion. Module functions normally, irrespective of CPU emulation state.

Soft Stop Mode: Peripheral gracefully halts operations. The peripheral halts operation at a point that makes sense both to the internal DMA/data access operation and to the pin interface as described below, after finishing packet reception or transmission in progress:

∙DMA bus DMA master: DMA bus requests in progress are allowed to complete (DMA bus has no means to throttle command in progress from the Master) DMA bus requests that correspond to the same network packet are allowed to complete. No new DMA bus requests will be generated on the next new packet.

∙Configuration bus MMR interface: All MMR configuration bus requests are serviced as normal.

∙Events/interrupts: New events/interrupts are not generated to the CPU for newly arriving packets. Current transactions are allowed to finish and may cause an interrupt upon completion.

∙Slave pin interface: The pin interface functions as normal. If buffering is available in the peripheral, the peripheral services externally generated requests as long as possible. When the internal buffers are consumed, the peripheral will retry incoming network packets in the physical layer.

∙Master pin interface: No new master requests are generated. Master requests in progress are allowed to complete, including all packets located in the physical layer transmit buffers.

Hard Stop Mode: Peripheral should halt immediately. This mode is not supported in the RapidIO peripheral.

2.3.11Initialization Example

2.3.11.1Enabling the SRIO Peripherals

When the device is powered on, the SRIO peripheral is in a disabled state. Before any SRIO specific initialization can take place, the peripheral needs to be enabled; otherwise, its registers cannot be written, and the reads will all return a value of zero.

/* Glb enable srio

*/

=0x00000001 ;

=0x00000001 ; //MMR_EN

=0x00000001 ; //PORT0_EN

=0x00000001 ; //LSU_EN

=0x00000001 ; //MAU_EN

=0x00000001 ; //TXU_EN

=0x00000001 ; //RXU_EN

=0x00000001 ; //PORT1_EN

=0x00000001 ; //PORT2_EN

=0x00000001 ; //PORT3_EN

SPRU976 | Serial RapidIO (SRIO) | 69 |