www.ti.com

|

|

| SRIO Registers |

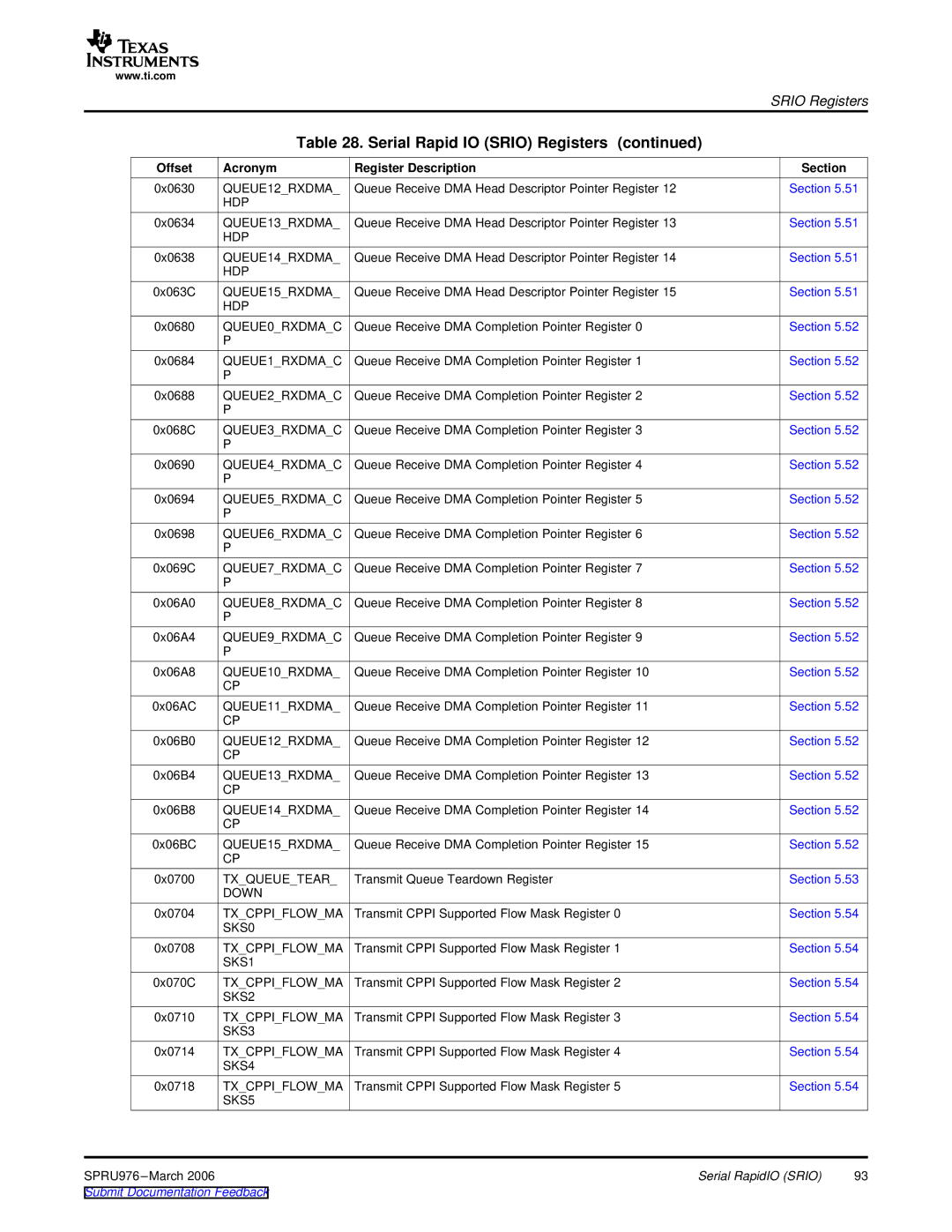

| Table 28. Serial Rapid IO (SRIO) Registers (continued) |

| |

Offset | Acronym | Register Description | Section |

0x0630 | QUEUE12_RXDMA_ | Queue Receive DMA Head Descriptor Pointer Register 12 | Section 5.51 |

| HDP |

|

|

0x0634 | QUEUE13_RXDMA_ | Queue Receive DMA Head Descriptor Pointer Register 13 | Section 5.51 |

| HDP |

|

|

0x0638 | QUEUE14_RXDMA_ | Queue Receive DMA Head Descriptor Pointer Register 14 | Section 5.51 |

| HDP |

|

|

0x063C | QUEUE15_RXDMA_ | Queue Receive DMA Head Descriptor Pointer Register 15 | Section 5.51 |

| HDP |

|

|

0x0680 | QUEUE0_RXDMA_C | Queue Receive DMA Completion Pointer Register 0 | Section 5.52 |

| P |

|

|

0x0684 | QUEUE1_RXDMA_C | Queue Receive DMA Completion Pointer Register 1 | Section 5.52 |

| P |

|

|

0x0688 | QUEUE2_RXDMA_C | Queue Receive DMA Completion Pointer Register 2 | Section 5.52 |

| P |

|

|

0x068C | QUEUE3_RXDMA_C | Queue Receive DMA Completion Pointer Register 3 | Section 5.52 |

| P |

|

|

0x0690 | QUEUE4_RXDMA_C | Queue Receive DMA Completion Pointer Register 4 | Section 5.52 |

| P |

|

|

0x0694 | QUEUE5_RXDMA_C | Queue Receive DMA Completion Pointer Register 5 | Section 5.52 |

| P |

|

|

0x0698 | QUEUE6_RXDMA_C | Queue Receive DMA Completion Pointer Register 6 | Section 5.52 |

| P |

|

|

0x069C | QUEUE7_RXDMA_C | Queue Receive DMA Completion Pointer Register 7 | Section 5.52 |

| P |

|

|

0x06A0 | QUEUE8_RXDMA_C | Queue Receive DMA Completion Pointer Register 8 | Section 5.52 |

| P |

|

|

0x06A4 | QUEUE9_RXDMA_C | Queue Receive DMA Completion Pointer Register 9 | Section 5.52 |

| P |

|

|

0x06A8 | QUEUE10_RXDMA_ | Queue Receive DMA Completion Pointer Register 10 | Section 5.52 |

| CP |

|

|

0x06AC | QUEUE11_RXDMA_ | Queue Receive DMA Completion Pointer Register 11 | Section 5.52 |

| CP |

|

|

0x06B0 | QUEUE12_RXDMA_ | Queue Receive DMA Completion Pointer Register 12 | Section 5.52 |

| CP |

|

|

0x06B4 | QUEUE13_RXDMA_ | Queue Receive DMA Completion Pointer Register 13 | Section 5.52 |

| CP |

|

|

0x06B8 | QUEUE14_RXDMA_ | Queue Receive DMA Completion Pointer Register 14 | Section 5.52 |

| CP |

|

|

0x06BC | QUEUE15_RXDMA_ | Queue Receive DMA Completion Pointer Register 15 | Section 5.52 |

| CP |

|

|

0x0700 | TX_QUEUE_TEAR_ | Transmit Queue Teardown Register | Section 5.53 |

| DOWN |

|

|

0x0704 | TX_CPPI_FLOW_MA | Transmit CPPI Supported Flow Mask Register 0 | Section 5.54 |

| SKS0 |

|

|

0x0708 | TX_CPPI_FLOW_MA | Transmit CPPI Supported Flow Mask Register 1 | Section 5.54 |

| SKS1 |

|

|

0x070C | TX_CPPI_FLOW_MA | Transmit CPPI Supported Flow Mask Register 2 | Section 5.54 |

| SKS2 |

|

|

0x0710 | TX_CPPI_FLOW_MA | Transmit CPPI Supported Flow Mask Register 3 | Section 5.54 |

| SKS3 |

|

|

0x0714 | TX_CPPI_FLOW_MA | Transmit CPPI Supported Flow Mask Register 4 | Section 5.54 |

| SKS4 |

|

|

0x0718 | TX_CPPI_FLOW_MA | Transmit CPPI Supported Flow Mask Register 5 | Section 5.54 |

| SKS5 |

|

|

SPRU976 | Serial RapidIO (SRIO) | 93 |

Submit Documentation Feedback |

|

|